国際特許分類[H01L23/532]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832) | 動作中の装置内の1つの構成部品から他の構成部品へ電流を導く装置 (7,814) | 半導体本体上に分離できないように形成された導電層及び絶縁層の多層構造からなる外部の相互接続を含むもの (2,851) | 材料に特徴のあるもの (313)

国際特許分類[H01L23/532]に分類される特許

71 - 80 / 313

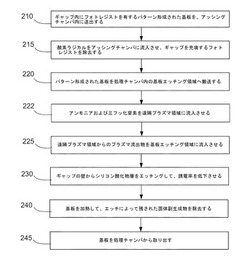

アッシュ後の側壁の回復

【課題】有効誘電率を増大させ、デバイスの性能を制限する可能性がある環境に低K薄膜を曝した後、より低い有効誘電率を維持する新しいプロセスを提供する。

【解決手段】集積回路の2つの導電性構成要素の間に存在する、有効誘電率を低下させる方法。その方法は、低K誘電体層の酸素が豊富な部分に対して選択的な気相エッチの使用を伴う。エッチング速度は、エッチプロセスが比較的高Kの酸素が豊富な部分を通過し、低K部分に達すると減じる。気相エッチプロセスが望ましい低K部分を容易に除去することはないため、エッチプロセスのタイミングを簡単に合わせることができる。

(もっと読む)

銅膜作製方法

【課題】下地層との密着性に優れた銅膜を製造する方法の提供。

【解決手段】成膜対象物上に下地層としてチタン膜を形成した後、この下地層を水素ガス雰囲気中で100℃以上200℃未満の温度で熱処理し、次いでその上に銅膜を作製する。このように銅膜を作製した後、さらに水素ガス雰囲気中で100℃以上200℃未満の温度で熱処理を行う。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】メモリセルトランジスタのゲート電極間の空隙の形状を最適化し、高性能、高信頼性を実現する不揮発性半導体記憶装置の製造方法。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板上に、第1のゲート絶縁膜、第1のフローティングゲート電極、第1のゲート間絶縁膜、第1のコントロールゲート電極、第1のゲートマスク絶縁膜の積層構造を有する複数のメモリセルゲート電極を形成する。メモリセルゲート電極の側壁部に保護膜を形成し、その一部を第1のコントロールゲート電極の側壁部の一部が露出するよう除去する。金属膜を形成し、熱処理により、金属膜と第1のコントロールゲート電極を反応させ第1の金属半導体化合物層を形成する。メモリセルゲート電極間を埋め込み、内部に空隙を有する層間絶縁膜であって、第1のコントロールゲート電極の上面よりも半導体基板から離れた位置に空隙の上端が位置する層間絶縁膜を形成する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】シリサイド工程によるゲート絶縁膜の金属汚染や、メモリセルのショートチャネル効果を抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、半導体基板と、前記半導体基板上に順に形成された第1絶縁層、電荷蓄積層、第2絶縁層、および制御電極を有し、前記電荷蓄積層の側面が傾斜面を有する複数のメモリセルトランジスタとを備える。さらに、前記装置は、前記メモリセルトランジスタの側面と、前記メモリセルトランジスタ間の前記半導体基板の上面に形成された第1の絶縁膜部分と、前記メモリセルトランジスタ間のエアギャップ上と前記メモリセルトランジスタ上に連続して形成された第2の絶縁膜部分と、を有する1層以上の絶縁膜を備える。さらに、前記メモリセルトランジスタ間の前記半導体基板の上面から前記エアギャップの下端までの第1距離は、前記メモリセルトランジスタの側面に形成された前記絶縁膜の膜厚よりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板における抵抗やコンタクト抵抗を低減させた半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、シリコン層と、シリコン層に形成され、第1不純物を含有する金属シリサイド層と、を備える。シリコン層は、金属シリサイド層が形成されていない領域において、第1不純物に起因するエンド・オブ・レンジ欠陥を有していない。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】配線抵抗の上昇や絶縁耐性の劣化を抑制しつつ、配線信頼性を確保する。

【解決手段】半導体装置100は、半導体基板と、半導体基板上に設けられた層間絶縁膜50と、層間絶縁膜50に埋め込まれた、Cuにより構成される配線10と、配線10の表層に設けられた、銅錯体を含有する表面層20と、を備える。配線10の表層に銅錯体を含有する表面層20を備えることにより、配線抵抗の上昇や絶縁耐性の劣化を抑制しつつ、配線信頼性を確保することができる。

(もっと読む)

電子部品用積層配線膜

【課題】 Moの持つSiバリヤ性、ITOコンタクト性という利点を維持しながら、耐酸化性を改善し、尚且つCuとの積層時や信号ケ−ブルの取り付け等の加熱工程を経ても低い電気低抵値を維持できる、電子部品用積層配線膜を提供する。

【解決手段】 基板上に金属膜を形成した電子部品用積層配線膜において、Cuでなる主導電層と、該主導電層の一方の面および/または他方の面を覆う被覆層からなり、該被覆層は原子比における組成式がMo100−XNiX、10≦X≦70で表され、残部不可避的不純物からなるMo−Ni合金である電子部品用積層配線膜。

(もっと読む)

貫通配線付き接合基板

【課題】貫通孔内に配した樹脂が熱膨張することによって電極を破損することを防止した貫通配線付き接合基板の提供。

【解決手段】

一面1aに電極層2が形成された第一基板1、及び電極層2と接合樹脂層3を介して、第一基板1と接合された第二基板4とを備えた貫通配線付き接合基板10Aであって、第一基板1の他面1b側から電極層2が露出するまで第一基板1を貫通する貫通孔5と、貫通孔5の内部において、貫通孔5の内側面5c及び電極層2を覆う貫通配線層6と、貫通配線層6を覆い貫通孔5の内部に充填された充填樹脂部7とを有し、充填樹脂部7を構成する樹脂のヤング率は、接合樹脂層3を構成する樹脂のヤング率よりも小さいことを特徴とする貫通配線付き接合基板10A。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1のnMIS形成領域1Aにnチャネル型MISFETQnを、半導体基板1のpMIS形成領域1Bにpチャネル型MISFETQpを、それぞれ形成してから、nチャネル型MISFETQnおよびpチャネル型MISFETQpを覆うように引張応力の窒化シリコン膜5を形成し、nMIS形成領域1AおよびpMIS形成領域1Bの窒化シリコン膜5に紫外線照射処理を施す。その後、nMIS形成領域1Aの窒化シリコン膜5を覆いかつpMIS形成領域1Bの窒化シリコン膜5を露出するマスク層6aを形成してから、pMIS形成領域1Bの窒化シリコン膜5をプラズマ処理することで、pMIS形成領域1Bの窒化シリコン膜5の引張応力を緩和させる。

(もっと読む)

71 - 80 / 313

[ Back to top ]