国際特許分類[H01L27/12]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体以外のもの,例.絶縁体本体 (2,168)

国際特許分類[H01L27/12]の下位に属する分類

薄膜または厚膜受動構成部品と組合せたもの

国際特許分類[H01L27/12]に分類される特許

81 - 90 / 2,168

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

印刷可能半導体素子を製造して組み立てるための方法及びデバイス

【課題】印刷可能半導体素子を製造するとともに、印刷可能半導体素子を基板表面上に組み立てるための方法及びデバイスを提供する。

【解決手段】デバイス、デバイス部品は、幅広いフレキシブル電子デバイス及び光電子デバイス並びにデバイスの配列を高分子材料を備える基板上に形成する。伸張形態で良好な性能が得られる伸縮可能な半導体構造及び伸縮可能な電子デバイスを形成する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

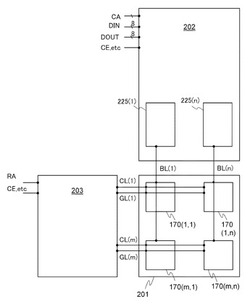

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料を用いたトランジスタと、第1の半導体材料とは異なる第2の半導体材料を用いたトランジスタと、容量素子とを有する複数のメモリセルを有し、書き込み期間にソース線に電源電位を供給する機能を有する電位切り替え回路を備えた半導体装置とする。これにより、半導体装置の消費電力を十分に抑えることができる。

(もっと読む)

半導体装置

【課題】トランジスタの損傷、破壊の発生を抑制することができる半導体装置を提供する。

【解決手段】第1の基板11上の第1の絶縁層12と、第1の絶縁層上のトランジスタ13と、トランジスタ上の第2の絶縁層14と、第2の絶縁層14に設けられた開口部を介して、トランジスタのソース領域又はドレイン領域に接続された第1の導電層15〜18と、第1の導電層上の第3の絶縁層38と、第3の絶縁層38上の第2の基板19と、を有し、トランジスタは、半導体層20と、第2の導電層22と、半導体層20と第2の導電層22の間に設けられた第4の絶縁層21とを有し、第1の絶縁層12、第2の絶縁層14、第3の絶縁層38及び第4の絶縁層21から選択された一つ又は複数は、トランジスタと重ならないように設けられた段差部を有する。

(もっと読む)

貼り合わせウェーハの製造方法及び貼り合わせSOIウェーハ

【課題】 本発明は、ベースウェーハ上の薄膜、特にはSOI層の膜厚均一性が向上された貼り合わせウェーハを量産レベルで製造することができる貼り合わせウェーハの製造方法を提供する。

【解決手段】 バッチ式イオン注入機を使用したイオン注入工程と、ボンドウェーハのイオン注入した表面とベースウェーハの表面とを直接あるいは絶縁膜を介して貼り合わせる貼り合わせ工程と、イオン注入層でボンドウェーハを剥離させることにより、ベースウェーハ上に薄膜を有する貼り合わせウェーハを作製する剥離工程を有する貼り合わせウェーハの製造方法において、イオン注入工程におけるボンドウェーハへのイオン注入を複数回に分けて行うものとし、各回のイオン注入後に、ボンドウェーハを所定の回転角度だけ自転させ、自転させた配置位置で次のイオン注入を行うことを特徴とする貼り合わせウェーハの製造方法。

(もっと読む)

薄膜デバイスの製造方法、薄膜デバイス基材、及び、薄膜デバイス

【課題】従来公知のデバイス素子の形成手法を広く一般的に使用でき、かつ、品質にも優れた薄膜デバイスの製造方法を提供する。

【解決手段】一例として、強磁性体層11の表面側に絶縁層12を積層して、可撓性の薄膜デバイス基材を得る積層工程と、薄膜デバイス基材を支持するために、前記強磁性体層の裏面側に、強磁性体層と引き合う磁性平板21を磁力で密着させる支持板密着工程と、薄膜デバイス基材の前記絶縁層上にデバイス素子13を形成する素子形成工程と、強磁性体層の裏面側から磁性平板21を取り外す支持板離脱工程と、を備える薄膜デバイスの製造方法である。

(もっと読む)

複合基板

【課題】 外部衝撃による半導体層の損傷を抑制することのできる、生産性の高い複合基板を提供する。

【解決手段】 複合基板1は、絶縁性材料からなり、中央に位置する主部11および周縁に位置する周縁部12を有する支持基板10と、前記主部11の上面11aに位置する半導体層20とを含み、周縁部12の上面12aの算術平均粗さは、主部11の上面11aの算術平均粗さに比べて大きくなっている。

(もっと読む)

半導体基板または半導体装置の製造方法

【課題】平面形状の面積が大きい平板状空洞を備えた半導体基板または半導体装置の製造方法を提供することにある。

【解決手段】半導体基板1の表面にホール4を複数形成する。この後、減圧下において非酸化性雰囲気のアニール処理を行う。アニール処理により、半導体基板1の表面を半導体の表面マイグレーションを利用して平坦化し、基板内部に平板状空洞6を形成する。このアニール処理の際に、ホール4の開口部が閉じた後に減圧下の状態のまま半導体のソースガスを供給する。

(もっと読む)

半導体基板、その製造方法及び半導体装置

【課題】実施形態は、異なる種類の半導体素子のそれぞれに適合した半導体層が1つの絶縁膜上に設けられた半導体基板、その製造方法及び半導体装置を提供する。

【解決手段】実施形態に係る半導体基板は、第1絶縁層と、前記第1絶縁層の上に設けられた第1半導体層と、前記第1半導体層の上に選択的に設けられた第2絶縁層と、前記第2絶縁層を介して前記第1半導体層の上に設けられた第2半導体層と、を備える。さらに、前記第1半導体層の表面から前記第1絶縁膜に至る深さに延設され、前記第1半導体層における前記第1絶縁層と前記第2絶縁層との間の部分と、前記第1半導体層の残りの部分と、を電気的に分離した第3絶縁層を備える。

(もっと読む)

81 - 90 / 2,168

[ Back to top ]