国際特許分類[H01L27/12]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体以外のもの,例.絶縁体本体 (2,168)

国際特許分類[H01L27/12]の下位に属する分類

薄膜または厚膜受動構成部品と組合せたもの

国際特許分類[H01L27/12]に分類される特許

71 - 80 / 2,168

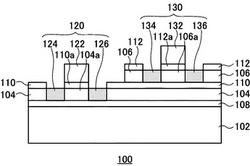

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインが、第1半導体結晶層を構成する原子とニッケル原子との化合物、第1半導体結晶層を構成する原子とコバルト原子との化合物または第1半導体結晶層を構成する原子とニッケル原子とコバルト原子との化合物からなり、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、第2半導体結晶層を構成する原子とニッケル原子との化合物、第2半導体結晶層を構成する原子とコバルト原子との化合物、または、第2半導体結晶層を構成する原子とニッケル原子とコバルト原子との化合物からなる半導体デバイスを提供する。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装

置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び

有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電

層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあ

わせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

積層体とその製造方法及びそれを用いたデバイス構造体の製造方法

【課題】各種デバイスを積層するための基材とするためのポリイミドフィルムと支持体との積層体であって、デバイス作製時の高温プロセスにおいても剥がれることなく、しかもポリイミドフィルム上にデバイスを作製した後には容易に支持体からポリイミドフィルムを剥離することができる積層体を提供する。

【解決手段】ポリイミドフィルム6として、少なくとも支持体1に対向させる面にプラズマ処理が施されたフィルムを用い、支持体1とポリイミドフィルム6とが対向する面の少なくとも一方にカップリング剤を用いて、接着剥離強度は異なり表面粗さは略同一である良好接着部分と易剥離部分とを形成するパターン化処理を施した後、重ね合わせて加圧加熱処理することとし、ポリイミドフィルム6は、70モル%以上がベンゾオキサゾール構造を有する芳香族ジアミン類を主成分とするジアミン類とテトラカルボン酸類との反応によって得られる。

(もっと読む)

一時的接着を利用して半導体構造を製造するためのプロセス

【課題】半導体構造を製造するためのプロセスを提供すること。

【解決手段】本発明は、半導体構造を製造するためのプロセスに関し、以下のステップ、すなわち、シード基板(1)と、シード基板(1)を覆う脆弱化された犠牲層(2)とを備えるハンドル基板(1、2)を提供するステップ(E1)と、ハンドル基板(1、2)をキャリア基板(3)と接合するステップ(E2)と、キャリア基板(3)を任意選択で処理するステップ(E3)と、犠牲層(2)においてハンドル基板を分離し、半導体構造を形成するステップ(E4)と、シード基板(1)上に存在する犠牲層(2)の残留物があればそれを除去するステップ(E5)とを備えることを特徴とする。

(もっと読む)

半導体製造装置及び製造方法

【課題】貼り合わせプロセス時のウェハの局所的な変形を低減する半導体製造装置及び製造方法を提供すること。

【解決手段】実施の形態によれば、第1及び第2の半導体基板の接合面同士を一点接触させて周囲に接合を進展させて第1及び第2の半導体基板を全面で接合する半導体製造装置である。半導体製造装置は、第1の半導体基板の外周部分を支持するステージと、第2の半導体基板の接合面とステージに支持された第1の半導体基板の接合面とを対向させて、第2の半導体基板を保持する基板支持装置と、接合面同士を対向させた第1及び第2の半導体基板の法線方向の同軸上に、法線方向に移動可能にそれぞれ配置された第1及び第2の圧子と、第1の圧子を第1の半導体基板の接合面と反対側の面と接触させ、その後、第2の圧子で第2の半導体基板の接合面とは反対側の面の一点を予め定められた圧力で加圧して接合開始点を形成するコントローラと、を備える。

(もっと読む)

粗面化処理透明SOIウェーハの製造方法

【課題】本発明は、ウェーハにかかる負荷を低減させ、かつ、破損品の発生を大きく低減させ、歩留まりを向上させる粗面化処理透明SOIウェーハの製造方法を提供する。

【解決手段】透明絶縁性ウェーハ上にシリコン薄膜を有するSOIウェーハのシリコン薄膜側を、真空チャック又は静電チャックを用いて保持し、前記SOIウェーハの透明絶縁性ウェーハ側の表面にブラスト加工を施す粗面化処理透明SOIウェーハの製造方法を提供する。

(もっと読む)

薄型太陽電池の製造方法

【課題】薄型基板形成時の切断歩留りの高い薄型太陽電池の製造方法を提供すること。

【解決手段】シリコンインゴット201の表面より深い位置に歪み層202を形成し、歪み注入領域近傍となる位置にH元素注入層203を形成し、加熱処理により歪み層202の近傍にH元素起因の空孔層204を形成し、熱衝撃により薄型シリコン基板205をシリコンインゴット201から分離することにより、良質な空孔層を形成でき、基板を分離もしくは切断する際に、不良率が約50%以下というより高い切断歩留りを確保することができる。

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法

【課題】大面積のアクティブ面積を有するSOI基板を製造する。

【解決手段】Siを含む基板の一つの面の一部の上方に、SiGeを含む第1の層と、Siを含む第2の層とを基板側からこの順に配置する積層部を形成する工程(a)と、積層部の上方と基板の積層部が形成された領域とは異なる領域の上方とにまたがる第3の層を形成する工程(b)と、積層部の上方に位置する第3の層及び第2の層の各一部をエッチングすることにより、第1の層の一部を露出させる工程(c)と、工程(c)において露出した第1の層を、基板の第1の面に沿った方向にエッチングする工程(d)と、工程(c)においてエッチングされた第2の層を、基板の第1の面に沿った方向にエピタキシャル成長させる工程(e)と、積層部が形成された領域の基板と、第2の層との間にSiO2を含む第4の層を形成する工程(f)と、を含む。

(もっと読む)

ウェーハ接合強度検査装置及び方法

【課題】接合ウェーハを破壊することなく、接合界面に間隙が生じていない場合であっても、局所的な接合部の接合強度を検査することができる検査装置を提供する。

【解決手段】ウェーハ接合強度検査装置100は、接合ウェーハ200を保持する試料ステージ160と、テラヘルツ波を発生するテラヘルツ波発生器151と、接合ウェーハ200を透過又は反射したテラヘルツ波を検出するテラヘルツ波検出器157と、テラヘルツ波検出器157によって検出したテラヘルツ波より接合ウェーハ200のTHz波特性を演算する演算部と、を有する。演算部は、予め求めた基準試料のTHz波特性と接合強度の間の関係から、検査対象の接合ウェーハのTHz波特性に対応する接合強度を演算する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料を用いたトランジスタと、第1の半導体材料とは異なる第2の半導体材料を用いたトランジスタと、容量素子とを有する複数のメモリセルを有し、書き込み期間にソース線に電源電位を供給する機能を有する電位切り替え回路を備えた半導体装置とする。これにより、半導体装置の消費電力を十分に抑えることができる。

(もっと読む)

71 - 80 / 2,168

[ Back to top ]