国際特許分類[H01L27/12]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体以外のもの,例.絶縁体本体 (2,168)

国際特許分類[H01L27/12]の下位に属する分類

薄膜または厚膜受動構成部品と組合せたもの

国際特許分類[H01L27/12]に分類される特許

41 - 50 / 2,168

SOI基板の作製方法

【課題】表面のP−V値が小さく、かつ、高い結晶性を有する半導体薄膜層を備えたSOI基板の作製方法を提供する。

【解決手段】半導体薄膜層の結晶性を高く保つため、水素イオン添加処理中の半導体基板の温度を200℃以下に抑制した。加えて、水素イオン添加処理後の半導体基板を100℃以上400℃以下に保持した状態で半導体基板に対してプラズマ処理を行うことにより、水素イオン添加処理により生じる、半導体薄膜層の分離に対して寄与度の高いSi−H結合を残存させたまま、半導体薄膜層の分離に対して寄与度の低いSi−H結合を低減した。

(もっと読む)

半導体基板の製造方法および半導体装置の製造方法

【課題】エッジ部に形成される段差部の傾斜を緩やかにできるSON構造を有する半導体基板の製造方法およびその半導体基板を用いた半導体装置の製造方法を提供する。

【解決手段】第1ホール群13の外周部に第1ホール11より直径D2が小さく間隔W2が大きな第2ホール群14を形成し、その後の水素雰囲気の高温アニールで平板状の空洞を形成する。

(もっと読む)

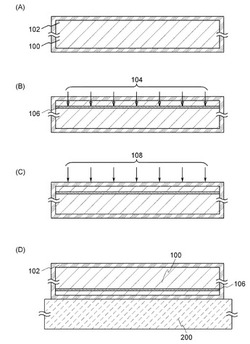

半導体装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装

置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び

有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電

層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあ

わせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

貼り合わせウェーハの製造方法

【課題】貼り合わせウェーハを製造する際、貼り合わせ直後にウェーハ周辺部に発生したボイドの個数・総面積を効率良く低減することができる貼り合わせウェーハの製造方法を提供する。

【解決手段】ボンドウェーハの表面とベースウェーハの表面とを、直接あるいは絶縁膜を介して貼り合わせた後、前記ボンドウェーハを薄膜化して貼り合わせウェーハを作製する貼り合わせウェーハの製造方法において、前記ボンドウェーハとベースウェーハの貼り合わせ後、30℃以上60℃以下の温度範囲で所定時間保持した後に、前記ボンドウェーハの薄膜化を行うことを特徴とする貼り合わせウェーハの製造方法。

(もっと読む)

SOIウエーハの製造方法

【課題】 リーク電流の発生や酸化膜耐圧の劣化等を抑制しながらも、十分なゲッタリング能力を有するSOIウエーハの製造方法を提供することを目的とする。

【解決手段】 少なくとも、ベースウエーハまたはボンドウエーハのいずれか一方の表面から、シリコン中で電気的に不活性である中性元素をイオン注入してイオン注入ダメージ層を形成する工程を備えるSOIウエーハの製造方法において、前記イオン注入ダメージ層形成工程における中性元素のイオン注入は、ドーズ量を1×1012atoms/cm2以上1×1015atoms/cm2未満として行うSOIウエーハの製造方法。

(もっと読む)

貼り合わせ基板の貼り合わせ面の評価方法

【課題】貼り合わせ面が露出していないブリスター部分の貼り合わせ面を、直接的に観察することのできる評価方法を提供することを目的とする。

【解決手段】支持基板と、該支持基板に貼り合わされた薄膜とを有する貼り合わせ基板の貼り合わせ面の評価方法であって、前記貼り合わせ基板に存在するブリスター部分の薄膜を除去することによって該ブリスター部分の貼り合わせ面を露出させ、該露出した貼り合わせ面を分析することを特徴とする貼り合わせ基板の貼り合わせ面の評価方法。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】半導体層を効率的に、かつ十分な接合力で基板上に接合し、断線することなく半導体層から基板へ至る配線を形成できる半導体装置の提供。

【解決手段】第1基板上に形成された半導体層を第2基板に移設して半導体装置を製造する方法であって、前記第2基板上に塗布されたフォトレジストを前記半導体層に接着する工程と、前記フォトレジストを露光する工程と、前記フォトレジストに接着された前記半導体層から前記第1基板を除去する工程と、前記フォトレジストを露光する工程と、前記露光されたフォトレジストをパターニングする工程とを含み、前記パターニングによって、前記第2基板と接合している前記フォトレジストの下面の縁部から前記フォトレジストの上面の縁部にわたって、前記上面の縁部に近づくにつれて前記フォトレジストの厚さが増大する傾斜した側面を前記フォトレジストに生成する。

(もっと読む)

電子デバイスの製造方法

【課題】転写歩留まりを向上することが可能な電子デバイスの製造方法を提供することを目的とする。

【解決手段】薄膜トランジスタ(TFT)19の製造方法において、スタンプ5の半導体膜8および絶縁膜9が形成される側の面とは反対側の面5aにガスバリア層7が形成されている。そのため、ガスバリア層7側からスタンプ5を空気で加圧する際に、スタンプ5の半導体膜8および絶縁膜9が形成される側の面とは反対側の面5aから、半導体膜8および絶縁膜9が形成される面に、加圧した空気が抜けにくくなる。これにより、スタンプ5を基板1に押し付けることを持続することができるので、スタンプ5に形成された半導体膜8および絶縁膜9と基板1との密着性を増すことができる。したがって、基板1に転写されない半導体膜8および絶縁膜9が減少し、薄膜転写の歩留まりを向上させることができる。

(もっと読む)

化合物半導体の形成方法

【課題】高電圧駆動素子の為にSiCやGaNの基板の簡素化が重要な課題となっている。

Si基板上のシリコン酸化膜の上に単結晶のSiC膜やGaN膜に形成したMOSFETなどの素子をアニールする手法を開示する。

【解決手段】光学ランプからの光をレンズで集光する手段、或いはレーザ光など高温度を発生させる手段によりSiCなど化合物半導体の表層部はSi基板の融点を越えるような高温度として、Si基板部はその融点よりも十分低い温度となるような冷却部を設けてSi基板を保持するステージを設けたことを特徴とするアニーリング装置。

(もっと読む)

41 - 50 / 2,168

[ Back to top ]