国際特許分類[H01L27/12]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体以外のもの,例.絶縁体本体 (2,168)

国際特許分類[H01L27/12]の下位に属する分類

薄膜または厚膜受動構成部品と組合せたもの

国際特許分類[H01L27/12]に分類される特許

61 - 70 / 2,168

半導体基板の再生方法、再生半導体基板の作製方法、及びSOI基板の作製方法

【課題】半導体基板の再生に適した方法を提供する。

【解決手段】損傷半導体領域と絶縁層とを含む凸部が周縁部に存在する半導体基板に対し、絶縁層を除去するエッチング処理と、硝酸、硝酸によって酸化された半導体基板を構成する半導体材料を溶解する物質、半導体材料の酸化速度及び酸化された半導体材料の溶解速度を制御する物質、及び亜硝酸を含み、亜硝酸の濃度が10mg/l以上1000mg/l以下である混合液を用いて、未損傷の半導体領域に対して損傷半導体領域を選択的に除去するエッチング処理と、を行うことで半導体基板を再生する。

(もっと読む)

単結晶の半導体層を支持基板上に転写する方法

【課題】単結晶の半導体層を支持基板上に転写し、転写された層がもはや脆化注入によって生成される可能性のある結晶欠陥を含まない方法を提供する。

【解決手段】単結晶の半導体層3を支持基板上に転写する方法に関し、(a)ドナー基板31に注入種を注入するステップと、(b)ドナー基板31を支持基板に接合するステップと、(c)層3を支持基板上に転写するためにドナー基板31を破壊するステップと、前記単結晶の層3の第2の部分35の結晶格子の秩序を乱すことなしに、転写されるべき単結晶の層3の部分34が非晶質にされるステップであり、部分34、35が、それぞれ、単結晶の層3の表面部分および埋め込み部分であるステップと、非晶質の部分34が500℃未満の温度で再結晶化されるステップであり、第2の部分35の結晶格子が再結晶化のための種結晶として働くステップとを含む。

(もっと読む)

薄膜デバイス用基板、及び薄膜デバイスの製造方法

【課題】密着性と剥離性とを兼ね備えた薄膜デバイス用基板、及び薄膜デバイスを歩留まり良く製造することができる製造方法を提供する。

【解決手段】支持基材上に、樹脂基材が設けられてなる薄膜デバイス用基材であって、支持基材側の樹脂基材の表面と、該樹脂基材の表面と接する面と、の界面が、JISK5600−5−7に準拠した付着性で、(A)0.03MPa以上0.12MPa以下の領域と、(B)0.14MPa以上の領域と、を有するように支持基材上の全部または一部に剥離調整層が設けられている。

(もっと読む)

半導体装置

【課題】プラスチック支持体を用いた半導体装置を提供する。

【解決手段】プラスチック支持体上に形成されたカラーフィルタと、前記カラーフィルタ

上に形成された接着層と、前記接着層上に形成された絶縁膜と、前記絶縁膜上に形成され

た薄膜トランジスタと、前記薄膜トランジスタ上に形成された発光素子とを有する。また

は、プラスチック支持体と、前記プラスチック支持体に対向する対向基板と、前記プラス

チック支持体と前記対向基板との間に保持された液晶とを有し、前記プラスチック支持体

上に形成されたカラーフィルタと、前記カラーフィルタ上に形成された接着層と、前記接

着層上に形成された絶縁膜と、前記絶縁膜上に形成された薄膜トランジスタとを有する。

(もっと読む)

固体撮像装置及びその製造方法、電子機器

【課題】画素分離部の幅を縮小することや光電変換部の面積の拡大することを可能にする固体撮像装置を提供する。

【解決手段】第1導電型の電荷蓄積領域23を含む光電変換部及び画素トランジスタTr1から成る画素38と、画素38が複数配列された画素領域と、この画素領域内の隣接する画素38間の半導体層22に設けられたトレンチ42の内壁部に形成された、エピタキシャル成長による第1導電型の半導体層43と、この第1導電型の半導体層43の内部に形成され、隣接する画素38の電荷蓄積領域23を分離する、画素分離部41とを含んで、固体撮像装置21を構成する。

(もっと読む)

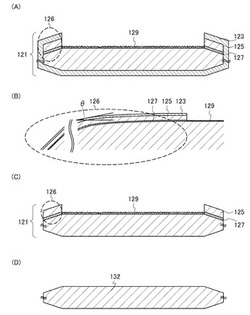

半導体装置の作製方法

【課題】 大面積のガラス基板上に薄膜からなる集積回路を形成し、他の基体に転写して分断を行い、接触、好ましくは非接触でデータの受信または送信が可能な微細なデバイスを大量に効率よく作製する方法を提供することを課題とする。特に薄膜からなる集積回路は、非常に薄いため移動時に飛んでしまう恐れがあり、取り扱いが難しかった。

【解決手段】 本発明は、剥離層に達する多数の穴または多数の溝を設け、穴(または溝)およびデバイス部に重ならない領域にパターン形状を有する材料体を設けた後、ハロゲン化フッ素を含む気体又は液体を導入して、前記剥離層を選択的に除去する。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインと、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、同一の導電性物質からなり、当該導電性物質の仕事関数ΦMが、数1および数2の少なくとも一方の関係を満たす。

(数1) φ1<ΦM<φ2+Eg2

(数2) |ΦM−φ1|≦0.1eV、かつ、|(φ2+Eg2)−ΦM|≦0.1eV

ただし、φ1は、N型半導体結晶層の電子親和力、φ2およびEg2は、P型半導体結晶層の電子親和力および禁制帯幅。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインが、第1半導体結晶層を構成する原子とニッケル原子との化合物、第1半導体結晶層を構成する原子とコバルト原子との化合物または第1半導体結晶層を構成する原子とニッケル原子とコバルト原子との化合物からなり、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、第2半導体結晶層を構成する原子とニッケル原子との化合物、第2半導体結晶層を構成する原子とコバルト原子との化合物、または、第2半導体結晶層を構成する原子とニッケル原子とコバルト原子との化合物からなる半導体デバイスを提供する。

(もっと読む)

半導体装置の製造方法、半導体装置、SOI基板の製造方法およびSOI基板

【課題】SOI基板のチャージ蓄積による不良を抑制する。

【解決手段】まず、シード基板100の一面に、シード基板100の表面と同一面を形成するように、開口部220を有する絶縁層200を形成する(絶縁層形成工程)。次いで、シード基板100の一面に接するように、支持基板300を貼り合せる(貼り合せ工程)。次いで、シード基板100または支持基板300の一方を薄板化することにより、当該薄板化基板からなる半導体層120を形成する(半導体層形成工程)。以上の工程により、SOI基板を準備する。次いで、半導体層120に半導体素子60を形成する(半導体素子形成工程)。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインと、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、同一の導電性物質からなり、当該導電性物質の仕事関数ΦMが、数1および数2の少なくとも一方の関係を満たす。

(数1) φ1<ΦM<φ2+Eg2

(数2) |ΦM−φ1|≦0.1eV、かつ、|(φ2+Eg2)−ΦM|≦0.1eV

ただし、φ1は、N型半導体結晶層の電子親和力、φ2およびEg2は、P型半導体結晶層の電子親和力および禁制帯幅。

(もっと読む)

61 - 70 / 2,168

[ Back to top ]