国際特許分類[H01L29/41]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 電極 (8,931) | その形状,相対的大きさまたは配置に特徴のあるもの (5,475)

国際特許分類[H01L29/41]の下位に属する分類

整流,増幅またはスイッチされる電流を流すもの (1,983)

整流,増幅またはスイッチされる電流を流さないもの (2,575)

国際特許分類[H01L29/41]に分類される特許

41 - 50 / 917

半導体装置および半導体装置の製造方法

【課題】 寄生抵抗を低減可能な半導体装置を提供する。

【解決手段】 半導体装置は、第1半導体層の表面に沿って延びる突起(2)を有する第1半導体層(1)を含む。ゲート電極(12)は、突起の表面をゲート絶縁膜を挟んで覆う。第2半導体層(28, 45)は、突起のゲート電極により覆われる部分と別の部分の側面上に形成され、溝(31, 52)を有する。ソース/ドレイン領域(30, 46)は、第2半導体層内に形成される。シリサイド膜(33)は、溝内の表面を含め第2半導体層の表面を覆う。導電性のプラグ(37)は、シリサイド膜と接する。

(もっと読む)

パワー絶縁ゲート型電界効果トランジスタ

【課題】酸化物半導体を用いたパワー絶縁ゲート型電界効果トランジスタ(パワーMISFET)を提供する。

【解決手段】半導体層103を挟んでゲート電極105とドレイン電極102を形成し、ゲート電極105の側面に半導体層109を形成し、ゲート電極105の頂上部と重なる部分で、半導体層109とソース電極112が接する構造を有する。このようなパワーMISFETのドレイン電極とソース電極の間に500V以上の電源と負荷を直列に接続し、ゲート電極105に制御用の信号を入力して使用する。

(もっと読む)

窒化物半導体装置

【課題】ドレイン配線電極に起因する電流コラプス現象への影響が抑制され、且つ耐圧が向上された窒化物半導体装置を提供する。

【解決手段】窒化物半導体からなるデバイス層と、デバイス層上に互いに離間して配置されたソース電極及びドレイン電極と、ソース電極とドレイン電極間でデバイス層上に配置されたゲート電極と、デバイス層上に配置された層間絶縁膜と、ドレイン電極とゲート電極間において層間絶縁膜を介してデバイス層と対向して配置され、ドレイン電極と電気的に接続されたドレイン配線電極と、ゲート電極とドレイン電極間においてデバイス層上に層間絶縁膜を介してデバイス層と対向して配置されたドレイン電極に比べて低電位側のフィールドプレートとを備え、ドレイン配線電極下方の層間絶縁膜の膜厚が、フィールドプレート下方の層間絶縁膜の膜厚よりも厚い。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】多様な構造を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1の上方に形成された化合物半導体層2と、が設けられている。化合物半導体層2には、第1の不純物の活性化により発生した第1導電型のキャリアを含む第1の領域2aと、第1の不純物と同一種類の第2の不純物の活性化により発生したキャリアを、第1の領域2aよりも低濃度で含有する第2の領域2bと、が設けられている。

(もっと読む)

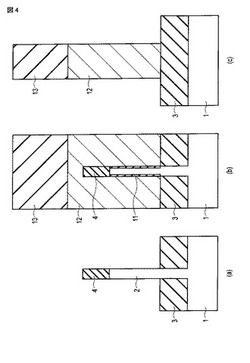

半導体素子

【課題】チャネル長Lが短く微細化が可能な、酸化物半導体を用いたトップゲート型の半

導体素子を提供することを課題とする。また、該半導体素子の作製方法を提供することを

課題とする。

【解決手段】絶縁表面上に酸化物半導体層と、酸化物半導体層上にソース電極層及びドレ

イン電極層と、酸化物半導体層、前記ソース電極層、及び前記ドレイン電極層上にゲート

絶縁層と、ゲート絶縁層上にゲート電極層とを有し、ソース電極層及びドレイン電極層は

側壁を有し、側壁は前記酸化物半導体層の上面と接する半導体素子である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置について、小型化を図りつつ、ドレイン耐圧を向上する。

【解決手段】ゲート電極20と、ゲート電極20と離間するソース電極24と、平面視でゲート電極20からみてソース電極24の反対側に位置し、かつゲート電極20と離間するドレイン電極22と、平面視でゲート電極20とドレイン電極22の間に位置し、絶縁膜26を介して半導体基板10上に設けられ、かつゲート電極20、ソース電極24およびドレイン電極22と離間する少なくとも一つのフィールドプレート電極30と、絶縁膜26中に設けられ、かつフィールドプレート電極30と半導体基板10を接続する少なくとも一つのフィールドプレートコンタクト40と、を備え、平面視でフィールドプレート電極30は、フィールドプレートコンタクト40からソース電極24側またはドレイン電極22側の少なくとも一方に延伸している。

(もっと読む)

半導体装置

【課題】リーク電流の少ないダイオードを提供する。

【解決手段】実施形態の半導体装置は、AlXGa1−XN(0<x<1)またはInyAl1−yN(0≦y≦1)からなる第1の半導体層2と、第1の半導体層の同一面上に、ノンドープ、n型又はp型のGaNからなる第1の電子誘起領域1、絶縁膜5とアノード電極7と、第1の電子誘起領域上にカソード電極を備え、第1の電子誘起領域、絶縁膜とアノード電極は第1の半導体層と接合し、絶縁膜は第1の半導体領域とアノード電極の間で、第1の半導体層と接合し、アノード電極と第1の半導体層との接合はオーミック接合であり、カソード電極と第1の電子誘起領域との接合はオーミック接合であることを特徴とする。

(もっと読む)

電界効果トランジスタ

【課題】ゲート電極とソース電極との間に印加される電圧がソース電極パッドの電気抵抗による電圧降下で低下することを防止でき、安定した動作を実現できる電界効果トランジスタを提供する。

【解決手段】このGaN HFETによれば、ボンディング部16Bの第2のパッド部16B‐2は、電極接続部16Aが含有する複数の接続部分19のうちの第2の方向(ソース電極12とドレイン電極11が対向している方向)の一端に配置された接続部分19の上記第2の方向の外端を電極延在方向へ延長した仮想延長線L1に関して第1のパッド部16B‐1とは反対側に位置している。第2のパッド部16B‐2に接続された第2のソース配線24のボンディング箇所の第2の方向の位置を電極接続部16Aのソース電極12との接続部分19の第2の方向の位置と重ならないようにして、ソース電極12からの電流が第2のソース配線24に流れにくくできる。

(もっと読む)

半導体装置及びその製造方法

【課題】通電領域表面の周辺の強電界の影響がナノワイヤに及び難くして、ホットキャリアの生成やオフリーク電流を低減する。半導体装置を高性能化する。

【解決手段】基板の表面よりも深い位置に配置され互いに対向する2つの側壁を有する導電膜と、導電膜の2つの側壁の側方に形成され互いに同じ導電型の半導体領域である第1及び第2の通電領域と、導電膜を貫通して2つの半導体領域どうしを接続し第1及び第2の通電領域の導電型とは逆導電型の半導体領域であるナノワイヤと、導電膜と前記ナノワイヤとの境界部に形成された絶縁膜と、を有することを特徴とする半導体装置。

(もっと読む)

半導体装置

【課題】接合終端領域における電界を緩和し、高耐圧化可能な半導体装置を提供する。

【解決手段】第1導電型の不純物を有する第1半導体領域と、第1半導体領域上に配置された、第1導電型と異なる第2導電型の第2半導体領域とを有する半導体基体には、コレクタ電極若しくはドレイン電極を有するスイッチング素子が形成された素子領域と、上方から見て半導体基体の最外周部に形成された、第2半導体領域の上面から第1半導体領域に達する終端トレンチと、終端トレンチの側壁および底面に形成された絶縁膜と、絶縁膜を介して溝の内側に埋め込まれた電極とを有し、溝の内側に埋め込まれた電極が第1半導体領域又はコレクタ領域若しくはドレイン電極と接続された等電位リングである。

(もっと読む)

41 - 50 / 917

[ Back to top ]