国際特許分類[H01L29/41]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 電極 (8,931) | その形状,相対的大きさまたは配置に特徴のあるもの (5,475)

国際特許分類[H01L29/41]の下位に属する分類

整流,増幅またはスイッチされる電流を流すもの (1,983)

整流,増幅またはスイッチされる電流を流さないもの (2,575)

国際特許分類[H01L29/41]に分類される特許

71 - 80 / 917

窒化物半導体装置及びその製造方法

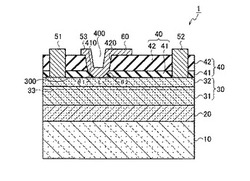

【課題】窒化物半導体層上の層間絶縁膜の開口部が、電界の集中が緩和される形状に安定して精度良く形成された窒化物半導体装置及びその製造方法を提供する。

【解決手段】窒化物半導体層30と、窒化物半導体層30上に配置された第1の絶縁膜41と、第1の絶縁膜41上に配置された第2の絶縁膜42と、窒化物半導体層30上に互いに離間して配置された第1及び第2の主電極51,52と、第1及び第2の主電極51,52間で第2の絶縁膜42上に配置され、第1及び第2の絶縁膜に設けられた開口部を介して窒化物半導体層に接続するフィールドプレート60とを備える窒化物半導体装置であって、開口部において、窒化物半導体層30の表面と第1の絶縁膜41の側面とのなす第1の傾斜角が、窒化物半導体層30の表面と第2の絶縁膜42の側面を延長した線とのなす第2の傾斜角よりも小さく形成されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電流コラプスを十分に抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1上方に形成された化合物半導体積層構造2と、化合物半導体積層構造2上方に形成されたゲート電極3、及び平面視でゲート電極3を間に挟む2個のオーミック電極4a及び4bと、が設けられている。更に、ゲート電極3上方に形成され、ゲート電極3並びにオーミック電極4a及び4bから絶縁分離されたフィールドプレート6が設けられている。フィールドプレート6のオーミック電極4a及び4bを互いに結ぶ方向における少なくとも一方の端部は、平面視で、オーミック電極4a及び4bとゲート電極3との間に位置する。

(もっと読む)

電界効果トランジスタ

【課題】動的な耐圧であるダイナミック耐圧の低下を抑制できるGaN系のHFETを提供する。

【解決手段】このGaN系のHFETでは、各ソース電極12の長手方向の長さL2が各ドレイン電極11の長手方向の長さL1よりも短く、ソース電極12の長手方向の両端12A,12Bがドレイン電極11の長手方向の両端11A,11Bよりも長手方向外方へ突出していない構成により、ソース電極12の端12A,12Bからドレイン電極11の端11A,11Bへ向かって電子流が集中することを回避できる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】閾値電圧のバラつきを抑制する溝トランジスタを提供する。

【解決手段】図1に示すように、表面に少なくとも一つ以上の溝部250を有している半導体基板40と、溝部250の側壁を覆うように形成されたゲート絶縁膜20と、溝部250に埋めこまれているゲート電極10と、半導体基板40の表面に形成され、ゲート電極10を介して互いに対向しているソースおよびドレイン150と、を含み、溝部250の側壁には、複数の凸凹100が形成されている。

(もっと読む)

グラフェンの合成方法並びに半導体装置及びその製造方法

【課題】触媒金属膜の任意の領域にグラフェンを選択的に合成しうるグラフェンの合成方法を提供する。

【解決手段】基板の所定の領域上に、触媒金属膜を形成する。次いで、触媒金属膜の側面に、触媒金属膜よりも触媒能の低い被覆膜を形成する。次いで、触媒金属膜の上面上に、触媒金属膜を触媒としてグラフェンを選択的に合成し、グラフェンチャネルを形成する。次いで、基板上に、グラフェンチャネルに接合されたソース電極及びドレイン電極を形成する。次いで、触媒金属膜及び被覆膜を除去する。次いで、グラフェンチャネル上に、ゲート絶縁膜及びゲート電極を形成する。

(もっと読む)

半導体装置

【課題】半導体膜と電極又は配線との接触抵抗を低減し、かつ半導体膜と電極又は配線と

の被覆率を改善し、特性を向上させた半導体装置を得ることを課題とする。

【解決手段】基板上にゲート電極と、前記ゲート電極上にゲート絶縁膜と、前記ゲート絶

縁膜上に第1のソース電極又はドレイン電極と、前記第1のソース電極又はドレイン電極

上に島状半導体膜と、前記島状半導体膜及び前記第1のソース電極又はドレイン電極上に

第2のソース電極又はドレイン電極とを有し、前記第2のソース電極又はドレイン電極は

前記第1のソース電極又はドレイン電極と接触しており、前記第1のソース電極又はドレ

イン電極及び第2のソース電極又はドレイン電極が前記島状半導体膜を挟みこんでいる半

導体装置及びその作製方法に関するものである。

(もっと読む)

半導体装置、半導体装置の製造方法、及び電子装置

【課題】縦型トランジスタのTDDB耐性を向上させ、かつ、閾値電圧がばらつくことも抑制する。

【解決手段】ゲート電極120の上端は、半導体基板100の表面よりも下に位置している。絶縁層340は、ゲート電極120上及びその周囲に位置する半導体基板100上に形成されている。絶縁層340は、第1絶縁膜342及び低酸素透過性絶縁膜344を有している。第1絶縁膜342は、例えばNSG膜であり、低酸素透過性絶縁膜344は、例えばSiN膜である。さらに、低酸素透過性絶縁膜344上には、第2絶縁膜346が形成されている。第2絶縁膜346は、例えばBPSG膜である。絶縁層340を形成した後、酸化雰囲気で処理することにより、縦型MOSトランジスタ20のTDDB耐性が向上する。また、絶縁層340が低酸素透過性絶縁膜344を有することにより、縦型MOSトランジスタ20の閾値電圧がばらつくことを抑制できる。

(もっと読む)

半導体デバイス及びその製造方法

【課題】グラフェンの特性を生かしつつ、高耐圧デバイスや紫外発光・受光デバイスを実現する。

【解決手段】半導体デバイスを、2次元構造のグラフェン電極2、3と、グラフェン電極のグラフェン端に結合した2次元構造のボロンナイトライド半導体層5とを備えるものとする。

(もっと読む)

シリコンカーバイドから製造されるモノリシックな縦型接合型電界効果トランジスタおよびショットキーバリアダイオード、および、その製造方法

【課題】縦型接合型電界効果トランジスタ(JFET)およびショットキーバリアダイオード(SBD)を備えるスイッチング素子を提供すること。

【解決手段】自己整合縦型接合型電界効果トランジスタを、エッチング注入ゲートおよび集積逆並列ショットキーバリアダイオードと組み合わせたスイッチング素子が、記載されている。ダイオードのアノードは、漂遊インダクタンスによる損失を低減するために、デバイスレベルでトランジスタのソースに接続される。SBDアノード領域におけるSiC表面は、SBDのターンオン電圧と関連するパワー損失が低減されるよう低いショットキーバリア高さを達成するために、乾式エッチングによって調整される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】高耐圧トランジスタ形成に適した半導体装置の新規な製造方法を提供する。

【解決手段】

半導体装置の製造方法は、シリコン基板に第1導電型第1領域と、第1領域に接する第2導電型第2領域を形成し、ゲート絶縁膜を形成し、第1領域と第2領域とに跨がるゲート電極を形成し、ゲート電極上から第2領域上に延在する絶縁膜を形成し、ゲート電極をマスクとし第2導電型不純物を注入してソース領域およびドレイン領域を形成し、ゲート電極および絶縁膜を覆って金属層を形成し熱処理を行って、ソース領域、ドレイン領域及びゲート電極にシリサイドを形成し、層間絶縁膜にソース領域、ドレイン領域、ゲート電極に達する第1、第2、第3コンタクトホール、及び絶縁膜に達する孔を形成し、第1〜第3コンタクトホール及び孔に導電材料を埋め込み、第1〜第3導電ビアと、孔の内部に配置された導電部材とを形成する。

(もっと読む)

71 - 80 / 917

[ Back to top ]