国際特許分類[H01L29/41]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 電極 (8,931) | その形状,相対的大きさまたは配置に特徴のあるもの (5,475)

国際特許分類[H01L29/41]の下位に属する分類

整流,増幅またはスイッチされる電流を流すもの (1,983)

整流,増幅またはスイッチされる電流を流さないもの (2,575)

国際特許分類[H01L29/41]に分類される特許

81 - 90 / 917

窒化物半導体装置およびその製造方法

【課題】窒化物半導体層とオーミック電極とのコンタクト抵抗を低減できる窒化物半導体装置を提供する。

【解決手段】Si基板10上に形成されたアンドープGaN層1,アンドープAlGaN層2と、アンドープGaN層1,アンドープAlGaN層2上に形成されたTi/Al/TiNからなるオーミック電極(ソース電極11,ドレイン電極12)とを備える。上記オーミック電極中の酸素濃度を1×1016cm−3以上かつ1×1020cm−3以下とする。

(もっと読む)

化合物半導体装置

【課題】 電流コラプスを抑制するとともに、高耐圧動作が可能な化合物半導体装置及びその製造方法を提供する。

【解決手段】 SiC基板10上に形成されたi−GaNバッファ層12と、i−GaNバッファ層12上に形成されたn−AlGaN電子供給層16と、n−AlGaN電子供給層16上に形成されたn−GaNキャップ層18と、n−GaNキャップ層18上に形成されたソース電極20及ドレイン電極22と、ソース電極20とドレイン電極22との間のn−GaNキャップ層18上に形成されたゲート電極26と、ソース電極20とドレイン電極22との間のn−GaNキャップ層18上に形成された第1の保護層24と、ゲート電極26とドレイン電極22との間の第1の保護層24に形成されたn−GaNキャップ層18に達する開口部28に埋め込まれ、第1の保護層24とは異なる絶縁層よりなる第2の保護層30とを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極とコンタクトとの間の短絡の発生を抑制する。

【解決手段】基板(2)に設けられた第1拡散領域(3)と、基板(2)に設けられた第2拡散領域(3)と、第1拡散領域(3)に接続された第1コンタクト(11)と、第2拡散領域(3)に接続された第2コンタクト(11)と、第1拡散領域(3)と第2拡散領域(3)の間に設けられたチャネル領域と、ゲート絶縁膜(6)を介してチャネル領域の上に設けられたゲート電極(5)とを具備する半導体装置を構成する。ゲート電極(5)は、第1コンタクト(11)と第2コンタクト(11)とに挟まれた第1領域(A−A’)と、第1領域と異なる第2領域(B−B’)とを備える。第1領域(A−A’)は、第1コンタクト側の第1側面と、第2コンタクト側の第2側面とを含む。第1側面は、第1コンタクトから離れる方向に傾斜する。第2側面は、第2コンタクトから離れる方向に傾斜する。

(もっと読む)

仮想ボディ・コンタクト型トライゲート

【課題】FETデバイスにおける閾値電圧をより良く制御できるデバイスの提供。

【解決手段】基板101と、基板101の上のSiGe層103と、SiGe層上の半導体層105と、基板、SiGe層及び半導体層に隣接した絶縁層109aと、絶縁層に隣接した一対の第1のゲート構造体111と、絶縁層上の第2のゲート構造体113とを含む電界効果トランジスタ(FET)と、FETを形成する方法である。絶縁層は、SiGe層の側面、並びに半導体層の上面、半導体層の下面及び導体層の側面に隣接していることが好ましい。SiGe層は、炭素を含むことが好ましい。一対の第1のゲート構造体が、第2のゲート構造体に対して実質的に横断方向にあることが好ましい。さらに、第1のゲート構造体の対は、絶縁層によりカプセル封入されることが好ましい。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型トランジスタの特性にばらつきが生じることを抑制する。

【解決手段】半導体基板100には縦型MOSトランジスタ20が形成されている。半導体基板100の表面上には、第1層間絶縁膜300及び第1ソース配線312が形成されている。第1ソース配線312は、第1層間絶縁膜300上に形成されており、平面視で縦型MOSトランジスタ20と重なっている。第1層間絶縁膜300にはコンタクト302が埋め込まれている。コンタクト302は、縦型MOSトランジスタ20のn型ソース層140と第1ソース配線312とを接続している。そして第1ソース配線312には、複数の開口316が形成されている。

(もっと読む)

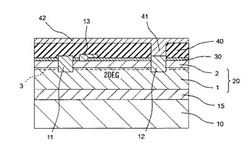

半導体装置

【課題】ソース・ドレイン間容量の低下と、電流コラプスの抑制とを両立することが可能な半導体装置を提供すること。

【解決手段】基板10と、基板10上に形成された窒化物半導体層11と、窒化物半導体層11上に設けられたソース電極24、ゲート電極28、及びドレイン電極26と、ゲート電極28、及びゲート電極28とドレイン電極26との間の窒化物半導体層11の表面を覆う絶縁膜20と、窒化物半導体層11上であって、ゲート電極28とドレイン電極26との間に設けられたフィールドプレート30と、を具備し、ゲート電極28とドレイン電極26との間の領域の絶縁膜20上におけるフィールドプレート30の幅Wは0.1μm以上であり、フィールドプレート30のドレイン電極26側の端部と、ドレイン電極26のゲート電極28側の端部との距離L1は、3.5μm以上であり、動作周波数が4GHz以下である半導体装置である。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果を抑制しつつ微細化を達成した半導体装置およびその作製方法を提供することを目的の一とする。

【解決手段】絶縁層にトレンチを形成し、トレンチの上端コーナー部と接する酸化物半導体膜に不純物を添加し、ソース領域およびドレイン領域を形成する。上記構造にすることで微細化することが可能である。また、トレンチを有することで、ソース電極層とドレイン電極層との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果を抑制することができる。

(もっと読む)

半導体装置

【課題】冷却効率を向上させることができる半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置10は、裏面に複数の凹部16を有するシリコン基板11と、この基板11の表面上に形成された半導体層12と、半導体層12の表面上に、互いに離間して形成されたドレイン電極13およびソース電極14と、ドレイン電極13とソース電極14との間の半導体層12上に形成されたゲート電極15と、複数の凹部16の内部を含むシリコン基板11の裏面全体に形成された裏面金属17と、を具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても高耐圧トランジスタのドレイン耐圧を向上させることができる半導体装置を提供する。

【解決手段】ゲート電極104Aの側面の側方下に位置する領域の半導体基板(活性領域)101の表面部が除去されて掘り下げ部121が形成されている。掘り下げ部121の側壁面及び底面の近傍に位置する部分の半導体基板101中に低濃度ドレイン領域105A2が形成されている。ゲート電極104Aの側面並びに掘り下げ部121の側壁面及び底面の一部を覆うように絶縁性サイドウォールスペーサ108Aが形成されている。絶縁性サイドウォールスペーサ108Aの外側で且つ掘り下げ部121の底面の近傍に位置する部分の半導体基板101中に、低濃度ドレイン領域105A2に囲まれるように高濃度ドレイン領域109A2が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチの対向する側面上に互いに離間されたゲート電極を有する半導体装置において、微細化に対応することができる半導体装置の製造方法を提供する。

【解決手段】トレンチ4を形成する工程およびゲート絶縁膜6を形成する工程では、トレンチ4のうち第2導電型層3と接する部分を中間部したとき、トレンチ4の対向する側面に形成されたゲート絶縁膜6の間隔において、トレンチ4の開口部に形成されている部分の間隔W1がトレンチ4の中間部に形成されている部分の間隔W2より狭くなるトレンチ4およびゲート絶縁膜6を形成する。そして、導電膜7aを形成する工程では、トレンチ4に導電膜7aで囲まれる空隙14を形成しつつ、導電膜7aを形成する。その後、ゲート電極7を形成する工程では、導電膜7aを異方性エッチングし、空隙14を介してトレンチ4の底面に形成された導電膜7aを除去してゲート電極7を形成する。

(もっと読む)

81 - 90 / 917

[ Back to top ]