国際特許分類[H01L29/41]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 電極 (8,931) | その形状,相対的大きさまたは配置に特徴のあるもの (5,475)

国際特許分類[H01L29/41]の下位に属する分類

整流,増幅またはスイッチされる電流を流すもの (1,983)

整流,増幅またはスイッチされる電流を流さないもの (2,575)

国際特許分類[H01L29/41]に分類される特許

21 - 30 / 917

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを提供する。

【解決手段】チャネル長方向の一方の側面においてソース電極層と接し、チャネル長方向の他方の側面においてドレイン電極層と接する酸化物半導体層を含むトランジスタとすることでソース電極層とドレイン電極層の間の電界を緩和して、短チャネル効果を抑制する。また、ゲート電極層のチャネル長方向の側面に導電性を有する側壁層を設けることで、当該導電性を有する側壁層がゲート絶縁層を介してソース電極層又はドレイン電極層と重畳し、実質的にLov領域を有するトランジスタとする。

(もっと読む)

半導体装置の製造方法

【課題】電気的特性が良好な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、シリコン基板の上面に、第1方向に延びる複数の凹部を形成する工程と、前記凹部が形成された前記シリコン基板を、弗素又は弗化物を含むガス中でプラズマ処理する工程と、前記プラズマ処理する工程の後で、前記シリコン基板を、水素を含むガス中で熱処理する工程と、前記熱処理する工程の後で、前記凹部の内面上に絶縁膜を形成する工程と、前記絶縁膜上に導電膜を形成する工程と、を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】性能の劣化を抑制することができる半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置10は、半導体層12、絶縁膜17、ゲート電極22、ドレイン電極19およびソース電極20、を具備する。半導体層12は、半絶縁性半導体基板11上に形成され、表面に、側壁が傾いたテーパ状のリセス領域18を有する。半導体層12は、活性層14を含む。絶縁膜17は、半導体層12上に形成されたものであり、リセス領域18を全て露出する貫通孔21を有する。貫通孔21は、側壁がリセス領域18の側壁の傾き角θ1より小さい角度θ2で傾いたテーパ状である。ゲート電極22は、リセス領域18および貫通孔21を埋めるように形成されたものである。ドレイン電極19およびソース電極20は、半導体層12上のうち、リセス領域18を挟む位置に形成されたものである。

(もっと読む)

半導体装置

【課題】耐圧を向上させることができる半導体装置を提供する。

【解決手段】半導体装置10は、ソース領域12a、複数の帯状のドレイン領域12b、チャネル領域、ソース電極16、ドレイン電極15、およびゲート電極17を具備する。ソース領域12aは、化合物半導体層11上に形成された平面状の領域である。複数の帯状のドレイン領域12bは、化合物半導体層11上に、互いに電気的に分離されるように形成される。チャネル領域は、ソース領域12aの一辺に接し、かつソース領域12aと複数のドレイン領域12bとの間に、互いに電気的に分離されるように形成される。ソース電極16は、ソース領域12a上の少なくとも一部に形成される。ドレイン電極15は、複数のドレイン領域12bに電気的に接続されるように形成される。ゲート電極17は、複数のチャネル領域に電気的に接続されるように形成される。

(もっと読む)

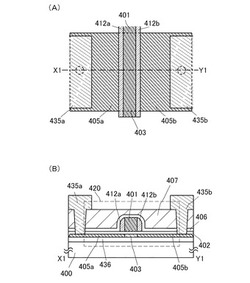

薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法

【課題】大型化に適した薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法を提供する。

【解決手段】フレキシブルな樹脂基板60に形成された薄膜トランジスタ200であって、周面の一部又は全部が導電性材料20により覆われたワイヤー10と、前記導電性材料を覆う絶縁膜30と、該絶縁膜を介して前記導電性材料上に形成された薄膜半導体40と、が一体的に構成されたゲート・チャネル一体形成部50を有し、該ゲート・チャネル一体形成部が前記樹脂基板の表面上又は内部の所定位置に設けられ、前記薄膜半導体の両側に第1及び第2の電極70、80が接続されて形成されたことを特徴とする。

(もっと読む)

第III族金属窒化物−絶縁半導体ヘテロ構造電界効果トランジスタ

【課題】ヘテロ構造電界効果トランジスタに関して、電流崩壊、ゲートリークおよび高温信頼性などの課題を解消する。

【解決手段】高電子移動度トランジスタ(HEMT)、金属−絶縁半導体電界効果トランジスタ(MISFET)あるいはこれらの組み合わせなどの集積回路(IC)デバイスの装置、方法およびシステムであって、該ICデバイスは、基板102上で形成されたバッファ層104と、アルミニウム(Al)と窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つを含み、バッファ層104上に形成されたバリア層106と、窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つとを含み、バリア層106上に形成されたキャップ108層と、キャップ層108に直接連結され、その層上に形成されたゲート118と、を含む。

(もっと読む)

横型素子を有する半導体装置

【課題】耐圧バラツキを抑制し、歩留りを向上させることが可能となる横型素子を有する半導体装置を提供する。

【解決手段】横型FWDなどの横型素子に備えられるSRFP21について、の不純物濃度を1×1018cm-3以上となるようにする。このように、横型FWD7などに備えられるSRFP21について、の不純物濃度を1×1018cm-3以上とすることにより、耐圧バラツキを抑制することが可能となり、的確に目標とする耐圧を得ることができる製品とすることが可能になる。したがって、製品の歩留りを向上させることが可能となる。

(もっと読む)

表示装置

【課題】2層構造の走査線を、絶縁膜を介して映像信号線が乗り越える際の、映像信号線の断線を防止する。

【解決手段】映像信号線が絶縁膜を介して走査線を乗り越える構成となっている。走査線10はAlCu合金を下層11とし、MoCr合金を上層12とする2層構造である。上層/下層の膜厚比を、0.4以上、1.0以下とすることによって、走査線10の断面において、電池作用によって上層12のエッチング速度が遅くなって、上層12の庇部が形成されることを防止する。これによって、走査線10に生じた庇部に起因して、映像信号線が走査線10との交差部において断線することを防止する。

(もっと読む)

半導体ウエハ、半導体ウエハ検査装置、及び半導体ウエハの検査方法

【課題】本発明は、半導体ウエハの検査において、半導体ウエハの裏面電極の端子としての機能を維持しつつ、半導体ウエハに過度の力がかかることを防止できる半導体ウエハ、半導体ウエハ検査装置、及び半導体ウエハの検査方法を提供することを目的とする。

【解決手段】本発明に係る半導体ウエハは、ダイシングラインを隔てて複数のチップが並ぶ半導体ウエハの表面側に形成された表面電極と、該半導体ウエハの裏面側に、該ダイシングラインを隔てて形成された複数の裏面電極と、該半導体ウエハの裏面側に、該ダイシングラインを跨いで該複数の裏面電極を電気的に接続する接続パターンと、を備える。該複数の裏面電極のうちの少なくともひとつは、該半導体ウエハのバイアホールを介して該表面電極と電気的に接続される。

(もっと読む)

半導体装置

【課題】低コンタクト抵抗を実現し得る半導体基板上の半導体層と電極配線層とのオーミック電極構造を提供する。

【解決手段】半導体基板106と、半導体基板106上に形成された第1のバリア層107と、第1のバリア層107上に形成された厚さ1nm以上40nm以下のチャネル層108と、チャネル層108の上に形成された第2のバリア層102と、少なくとも第2のバリア層102及びチャネル層108を厚さ方向に貫通する第1の電極領域109と、少なくとも第2のバリア層102及びチャネル層108を厚さ方向に貫通する第2の電極領域109とを備える半導体装置であって、少なくとも第1の電極領域109は、チャネル層108と接触する側の面が凹凸形状で構成されている。

(もっと読む)

21 - 30 / 917

[ Back to top ]