国際特許分類[H01L29/47]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 電極 (8,931) | 構成材料に特徴のあるもの (3,446) | ショットキー障壁電極 (987)

国際特許分類[H01L29/47]に分類される特許

41 - 50 / 987

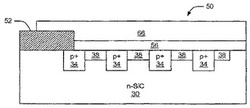

炭化ケイ素デバイス用のエッジ終端構造およびエッジ終端構造を含む炭化ケイ素デバイスの製造方法

【課題】炭化ケイ素デバイスの改善されたエッジ終端構造を提供する。

【解決手段】炭化ケイ素半導体デバイス用のエッジ終端構造は、少なくとも炭化ケイ素ベース接合を部分的に取り囲んで、炭化ケイ素層中において、所定間隔で配置された複数の同心円のフローティングガードリング34を有すると共に、フローティングガードリング上に設けられた絶縁層、及びフローティングガードリング同士の間でかつ炭化ケイ素層の表面の近くに設けられた炭化ケイ素表面電荷補償領域38を有する。炭化ケイ素層上に窒化ケイ素層56が設けられ、窒化ケイ素層上に有機保護層66が設けられる。酸化膜層が窒化ケイ素層と炭化ケイ素層の表面との間に存在してもよい。エッジ終端構造の形成・製造方法を開示されている。

(もっと読む)

半導体基板の製造方法及び半導体装置

【課題】基板に形成された窒化ガリウム系半導体で形成された半導体層におけるドーパント濃度がばらつくと、半導体層を用いた半導体装置の特性がばらつくので、半導体層におけるドーパント濃度のばらつきが抑えられた層を有する半導体基板を得る。

【解決手段】基板に、窒化ガリウム系半導体で形成された半導体層を形成する半導体層形成段階と、半導体層に、中性子線を照射して、半導体層に含まれるガリウム原子の一部をゲルマニウム原子に変換する照射段階と、を備える半導体基板の製造方法を提供する。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】 実施形態は、低損失な炭化珪素半導体装置の製造方法を提供することを目的とする。

【解決手段】 実施形態の炭化珪素半導体装置の製造方法は、炭化珪素基板にイオン注入する工程と、前記イオン注入がされた炭化珪素基板に第1の熱処理を行う工程と、前記第1の熱処理がされた炭化珪素基板に前記第1の熱処理より低温の第2の熱処理を行う工程と、を有することを特徴とする。

(もっと読む)

半導体装置

【課題】窒化ガリウム系半導体で形成された半導体層を有する半導体素子において、消費電力を増大させず、かつ、大型化することなく、半導体素子の電極に電圧をかけたときに発生する電流コラプス現象を抑制する。

【解決手段】窒化ガリウム系半導体が積層されて形成された半導体素子と、半導体素子に対して積層方向に形成され、外部からのエネルギーの入力なしで半導体素子に光を照射する自己発光体とを備える半導体装置を提供する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】SiC基板を用いて形成され、金属シリサイド膜と金属電極との密着性の向上する半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、炭化珪素と、炭化珪素上に形成され、第1の層、第1の層よりも低い炭素比率を有する第2の層を備える金属シリサイドと、金属シリサイド上に形成される金属電極を備え、第2の層が第1の層上に形成され、第2の層が金属電極に接し、第2の層中の金属シリサイドの平均粒径が、第1の層中の金属シリサイドの平均粒径よりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】高い逆方向耐圧VR及び低いリーク電流IRを維持したまま、順方向降下電圧VFを低くしたり、逆回復時間trrを短くしたりすることが可能な半導体装置を提供する。

【解決手段】n+型半導体層112とn−型半導体層114とを有する半導体基体110と、n−型半導体層114の表面に選択的に形成されたp+型拡散領域120と、n−型半導体層114及びp+型拡散領域120の表面上に形成され、n−型半導体層114との間でショットキー接合を形成し、p+型拡散領域120との間でオーミック接合を形成するバリアメタル層130とを備える半導体装置であって、半導体基体110には、n−型半導体層114の表面で濃度が最も高くなるように重金属としての白金が拡散されている。

(もっと読む)

半導体素子

【課題】III族窒化物半導体を用いて形成され、優れた特性を有する半導体素子を提供する。

【解決手段】半導体素子が、ワイドバンドギャップ材料を用いて電子を多数キャリアとするように構成されてなる第1半導体層の一方主面上に、それぞれが電気的に接続されてなる複数の単位アノード部、を有するアノード部と、それぞれが電気的に接続されてなる複数の単位カソード電極、を有するカソード部と、を備え、複数の単位アノード部のそれぞれと複数の単位カソード電極のそれぞれとが交互に配置された電極列が形成されてなり、複数の単位アノード部のそれぞれの、少なくとも第1半導体層と接合する部分が、所定の半導体材料を用いて正孔を多数キャリアとするように構成されてなる第2半導体層であり、第1半導体層と第2半導体層との接合部においてはP−N接合が形成されてなる、ようにした。

(もっと読む)

半導体素子

【課題】III族窒化物半導体を用いて形成され、優れた特性を有する半導体素子を提供する。

【解決手段】半導体素子が、電子を多数キャリアとするように構成されてなる第1半導体層の一方主面上に、それぞれが電気的に接続されてなる複数の単位アノード部、を有するアノード部と、それぞれが電気的に接続されてなる複数の単位カソード電極、を有するカソード部と、を備え、複数の単位アノード部のそれぞれと複数の単位カソード電極のそれぞれとが交互に配置された電極列が形成されてなり、複数の単位アノード部のそれぞれと第1半導体層との接合部がそれぞれ第1と第2の接合部からなり、第1接合部は、第1半導体層と接続する単位アノード部部分が正孔が多数キャリアの第2半導体層であるP−N接合部であり、第2接合部は、第1半導体層と接続する単位アノード部部分が金属によって構成されたショットキー接合部である、ようにした。

(もっと読む)

ダイオード、半導体装置およびMOSFET

【課題】 ダイオードにおけるスイッチング時の損失を低減することが可能な技術を開示する。

【解決手段】 本明細書で開示するダイオードは、カソード電極と、第1導電型の半導体からなるカソード領域と、低濃度の第1導電型の半導体からなるドリフト領域と、第2導電型の半導体からなるアノード領域と、金属からなるアノード電極を備えている。そのダイオードは、前記ドリフト領域と前記アノード領域の間に形成された、前記ドリフト領域よりも濃度が高い第1導電型の半導体からなるバリア領域と、前記バリア領域と前記アノード電極を接続するように形成された、前記バリア領域よりも濃度が高い第1導電型の半導体からなるピラー領域を備えている。そのダイオードでは、前記ピラー領域と前記アノード電極がショットキー接合している。

(もっと読む)

半導体装置

【課題】パワー半導体素子において、周辺の電界強度を緩和する構造を小さな面積で実現する。

【解決手段】周辺領域Qにおいては、半導体層との間に周辺層間絶縁層(絶縁層)を介して複数の多結晶シリコン層70が、ソース電極30から端部ドレイン電極41の間にかけて設けられる。多結晶シリコン層70には、その長手方向が水平方向から傾斜した(傾斜角θ、0<θ<90°)傾斜部が設けられている。多結晶シリコン層70の傾斜部においては、p型領域71と、n型領域72とが長手方向に交互に多数形成されている。

(もっと読む)

41 - 50 / 987

[ Back to top ]