国際特許分類[H01L29/47]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 電極 (8,931) | 構成材料に特徴のあるもの (3,446) | ショットキー障壁電極 (987)

国際特許分類[H01L29/47]に分類される特許

31 - 40 / 987

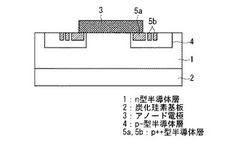

半導体装置およびその製造方法

【課題】本発明は、電界集中を緩和することで十分なサージ電流耐性を有した半導体装置およびその製造方法の提供を目的とする。

【解決手段】本発明にかかる半導体装置は、炭化珪素からなる第1導電型の半導体層としてのn型半導体層1と、n型半導体層1表層において、ショットキーダイオードの素子領域を平面視上囲んで形成された、第2導電型の第1不純物層としてのp++型半導体層5aと、n型半導体層1表層において、素子領域を、少なくともp++型半導体層5aの平面視上外側から囲んで形成された、第2導電型の第2不純物層としてのp++型半導体層5bと、p++型半導体層5a表層まで延設して素子領域上に形成されたアノード電極3とを備え、p++型半導体層5aの不純物濃度が1×1020cm-3以上である。

(もっと読む)

半導体装置及びその製造方法

【課題】薄型化された炭化シリコン基板による低抵抗化が可能な半導体装置及びその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、炭化シリコン基板と、半導体層と、絶縁膜と、補強基板と、第1の電極と、第2の電極とを備えている。半導体層は、炭化シリコン基板の第2の面上に設けられ、素子領域と素子領域よりも端部側の周辺領域とを有する。絶縁膜は、半導体層の周辺領域の表面上に設けられている。補強基板は、周辺領域における絶縁膜上に設けられている。第1の電極は、炭化シリコン基板の第1の面に接して設けられている。第2の電極は、素子領域の表面に接して設けられている。

(もっと読む)

窒化ガリウム結晶、ホモエピタキシャル窒化ガリウムを基材とするデバイス、及びその製造方法

【課題】ホモエピタキシャルLED、LD、光検出器又は電子デバイスを形成するために役立つGaN基板の形成方法の提供。

【解決手段】約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板上に配設された1以上のエピタキシャル半導体層を含むデバイス。かかる電子デバイスは、発光ダイオード(LED)及びレーザーダイオード(LD)用途のような照明用途、並びにGaNを基材とするトランジスター、整流器、サイリスター及びカスコードスイッチなどのデバイスの形態を有し得る。また、約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板を形成し、該基板上に1以上の半導体層をホモエピタキシャルに形成する方法及び電子デバイス。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】窒化物半導体を用いた電界効果トランジスタのしきい値電圧がより容易に制御できるようにする。

【解決手段】基板101の上に形成されたGaNからなる緩衝層102と、緩衝層102の上に形成されたAlGaNからなる障壁層103と、障壁層103の上に形成されたゲート電極104とを備える。また、障壁層103の上にゲート電極104を挟んでゲート電極104とは離間して形成されたソース電極105およびドレイン電極106を備える。加えて、障壁層103とゲート電極104との間に形成されたInAlNからなるキャップ層107を備える。

(もっと読む)

窒化物半導体素子及び製造方法

【課題】耐圧が高く、かつ、リーク電流が効果的に低減された窒化物半導体素子及びその製造方法を提供する。

【解決手段】ベース基板210と、ベース基板の上方に形成されたバッファ層280と、バッファ層280上に形成された活性層290と、活性層の上方に形成された少なくとも2つの電極292および294とを備え、バッファ層280は格子定数の異なる複数の窒化物半導体層を含む複合層を1層以上有し、複合層の少なくとも1層は、複数の窒化物半導体層のうち格子定数が最も大きい窒化物半導体層のキャリア領域に予め定められた濃度の炭素原子及び予め定められた濃度の酸素原子が意図的にドープされている窒化物半導体素子。

(もっと読む)

SiC半導体素子の製造方法

【課題】電極金属がSiC単結晶基板内に拡散するのを防止してオーミック電極を形成することができるSiC半導体素子の製造方法を提供する。

【解決手段】SiC基板上にオーミック電極を形成する工程を含むSiC半導体素子の製造方法において、

上記SiC基板にそれよりも欠陥密度の高いゲッタリング層を基板面に並行して形成した後に、該ゲッタリング層よりも該基板の外寄りに上記オーミック電極を形成することを特徴とするSiC半導体素子の製造方法。

(もっと読む)

SiCエピタキシャルウエハおよびそれを用いたSiC半導体素子

【課題】高品質かつ高信頼性の素子を作製できるSiCエピタキシャルウエハ、およびそれを用いて得られるSiC半導体素子を提供すること

【解決手段】4°以下のオフ角を有するSiC基板2と、SiC基板2の主面4に形成され、その表面10に0.5nm以上の高さのステップバンチング9が形成されたSiCエピタキシャル層3とを含むSiCエピタキシャルウエハ1において、ステップバンチング9の線密度を40cm−1以下にする。

(もっと読む)

高速回復整流器構造体の装置および方法

【課題】高速回復整流器構造体の装置および方法を提供する。

【解決手段】具体的には構造体は第1のドーパントの基板(120)を含む。第1のドーパントが低濃度ドープされた第1のエピタキシャル層(140)が基板に結合されている。第1の金属層(190)が第1のエピタキシャル層に結合されている。複数のトレンチ(175)が第1のエピタキシャル層内に窪んでおり、その各々が金属層と結合している。装置は各々第2のドーパント型がドープされた複数のウェルも含み、各ウェルは対応するトレンチの下に且つ隣接して形成されている。複数の酸化物層(170)が対応するトレンチの壁および底部上に形成されている。第1のドーパントがドープされた複数のチャネル領域が、2つの対応するウェル間の第1のエピタキシャル層内に形成されている。複数のチャネル領域(150)の各々は第1のエピタキシャル層より高濃度に第1のドーパントがドープされている。

(もっと読む)

不揮発性記憶素子及び不揮発性記憶装置並びにそれらの製造方法

【課題】良好な電気的特性が得られる不揮発性記憶素子及びその製造方法を提供する。

【解決手段】第1の配線103と、第1の配線103上に形成され、第1の配線103に接続される第1のプラグ107及び第2のプラグ108と、第1電極109、第2電極113、及び抵抗変化層112を有し、第1のプラグ107上に形成され、第1電極109が第1のプラグ107と電気的に接続されている抵抗変化素子114と、抵抗変化素子114上に形成され、第2電極113と電気的に接続されている第2の配線119と、第2のプラグ108上に形成され、第2のプラグ108と電気的に接続されている第3の配線121とを備え、第1のプラグ107の上面と第2のプラグ108の上面とが略同一平面内に形成され、かつ第2の配線119の上面と第3の配線121の上面とが略同一平面内に形成されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】多様な構造を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1の上方に形成された化合物半導体層2と、が設けられている。化合物半導体層2には、第1の不純物の活性化により発生した第1導電型のキャリアを含む第1の領域2aと、第1の不純物と同一種類の第2の不純物の活性化により発生したキャリアを、第1の領域2aよりも低濃度で含有する第2の領域2bと、が設けられている。

(もっと読む)

31 - 40 / 987

[ Back to top ]