国際特許分類[H01L29/78]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | 絶縁ゲートによって生じる電界効果を有するもの (29,475)

国際特許分類[H01L29/78]の下位に属する分類

薄膜トランジスタ (12,139)

浮遊ゲートを有するもの (4,374)

電荷トラッピングゲート絶縁体,例.MNOSメモリトランジスタ,を有するもの (4,374)

国際特許分類[H01L29/78]に分類される特許

11 - 20 / 8,588

炭化珪素半導体装置の製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

パワートランジスタ装置のための多層構造を作製する方法、ヘテロ接合電界効果トランジスタ装置のための多層構造を作製する方法、および窒化物系ヘテロ接合電界効果トランジスタ装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

炭化珪素半導体装置およびその製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

化合物半導体装置及びその製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置およびその製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

炭化珪素半導体装置の製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置、高電子移動度トランジスタ、および、複数のチャネルによりソースからドレインに電子を送るための方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

炭化珪素半導体装置の製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置

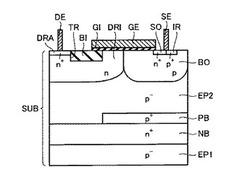

【課題】ハイサイド素子として用いても誤動作が少なく、かつオン耐圧およびオフ耐圧の双方を高く維持することのできる半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBの内部には、p-エピタキシャル領域EP1が、その主表面側にはp-エピタキシャル領域EP2が、その主表面側にはn型ドリフト領域DRIとp型ボディ領域BOとが形成されている。p-エピタキシャル領域EP1とp-エピタキシャル領域EP2との間には、これらの領域を電気的に分離するためにn+埋め込み領域NBが形成されている。n+埋め込み領域NBとp-エピタキシャル領域EP2との間には、p-エピタキシャル領域EP2よりも高いp型不純物濃度を有するp+埋め込み領域PBが形成されている。p+埋め込み領域PBは、n型ドリフト領域DRIとp型ボディ領域BOとの接合部の少なくとも直下に位置し、かつn型ドリフト領域DRIと接するドレイン領域DRAの直下を避けて配置されている。

(もっと読む)

半導体装置およびその製造方法

【課題】トンネルFETのオン電流の劣化を抑制しつつ、オフ電流を低減することが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、溝が形成された基板と、前記基板上の前記溝に隣接する位置にゲート絶縁膜を介して形成され、前記溝の反対側に位置する第1側面と、前記溝側に位置する第2側面とを有するゲート電極とを備える。さらに、前記装置は、前記ゲート電極の前記第1側面に形成された第1の側壁絶縁膜と、前記ゲート電極の前記第2側面と前記溝の側面に形成された第2の側壁絶縁膜とを備える。さらに、前記装置は、前記基板内において、前記ゲート電極の前記第1側面に対し前記第1の側壁絶縁膜側に形成された、第1導電型のソース領域と、前記基板内において、前記ゲート電極の前記第2側面と前記溝の側面に対し前記第2の側壁絶縁膜側に形成された、第2導電型のドレイン領域とを備える。

(もっと読む)

11 - 20 / 8,588

[ Back to top ]