国際特許分類[H01L29/78]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | 絶縁ゲートによって生じる電界効果を有するもの (29,475)

国際特許分類[H01L29/78]の下位に属する分類

薄膜トランジスタ (12,139)

浮遊ゲートを有するもの (4,374)

電荷トラッピングゲート絶縁体,例.MNOSメモリトランジスタ,を有するもの (4,374)

国際特許分類[H01L29/78]に分類される特許

31 - 40 / 8,588

半導体装置

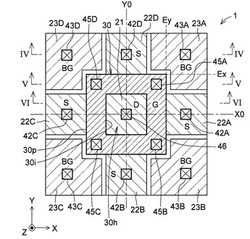

【課題】基板電位を安定化させることができる半導体装置を提供する。

【解決手段】半導体装置に含まれるFET素子1は、N角形をなす外周端部30pと貫通孔を形作る内周端部30iとを有する環状のゲート電極30を備える。またFET素子1は、貫通孔の直下方に形成された内側不純物拡散領域21と、ゲート電極30のN角形の辺の外側に形成された外側不純物拡散領域22A〜22Dと、ゲート電極30の頂点の外側に形成されたバックゲート領域23A〜23Dとを備える。バックゲート領域23A〜23Dは、ゲート電極30のN角形の辺のうちゲート電極30の頂点をなす2辺の延長線Ex,Eyの少なくとも一方を跨るように形成されている。

(もっと読む)

CMOS集積回路及び増幅回路

【課題】入力トランジスタの構造を櫛形構造にしてゲート抵抗を抑えつつ、NFの増大を防ぐことが可能なCMOS集積回路を提供する。

【解決手段】トランジスタは、ゲート配線から櫛歯状に延びて形成され、信号入力端子からの入力信号が供給されるゲート電極と、ゲート配線に対向した位置に形成されるソース配線から、ゲート電極の櫛歯の間に1つ起きに櫛歯状に延びて形成される、接地端子に接続されたソース電極と、ゲート配線に対向した位置に形成されるドレイン配線から、ゲート電極の櫛歯の間のソース電極が存在しない箇所に櫛歯状に延びて形成される、電源端子に接続されたドレイン電極と、を備え、ゲート電極と、ソース電極またはドレイン電極とは、重なり合う領域が存在しないことを特徴とする、CMOS集積回路が提供される。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】炭化珪素半導体装置に含まれる炭化珪素層の側面の面方位を特定の結晶面により近づけることができる炭化珪素半導体装置の製造方法を提供する。

【解決手段】基板1上に、主表面が設けられた炭化珪素層19が形成される。炭化珪素層19の主表面の一部を覆うマスク17が形成される。主表面に対して傾斜した側面SSが炭化珪素層19に設けられるように、マスク17が形成された炭化珪素層19の主表面に対して、塩素系ガスを用いた熱エッチングが行われる。熱エッチングを行う工程は、塩素系ガスの分圧が50%以下である雰囲気下で行われる。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル移動度の低下およびパンチスルーの発生が抑制され、かつ効率的に製造することができる半導体装置およびその製造方法を提供する。

【解決手段】MOSFET1は、{0001}面に対するオフ角が50°以上65°以下である側壁面20Aを有するトレンチ20が形成された基板10と、酸化膜30と、ゲート電極40とを備えている。基板10は、ソース領域14と、ボディ領域13と、ソース領域14との間にボディ領域13を挟むように形成されたドリフト領域12とを含む。ソース領域14およびボディ領域13はイオン注入により形成されている。ボディ領域13においてソース領域14とドリフト領域12との間に挟まれた内部領域13Aの主表面10Aに垂直な方向における厚みは、1μm以下である。ボディ領域13の不純物濃度は、3×1017cm−3以上である。

(もっと読む)

半導体ガスセンサ

【課題】従来技術を発展させた半導体ガスセンサを提供すること。

【解決手段】第1の端子部分が、半導体本体(20)の表面に設けられたパッシベーション層(30)を貫通する第1の成形部分(112)を有し、該第1の成形部分(112)は、参照電位に接続された導電性層(115)を備えた底面を有し、該第1の端子部分と制御電極(100)とは第1の接合材(130)を用いて電気的接続かつ摩擦接続的に結合されている。第2の端子部分と前記制御電極(100)とは第2の接合材(140)を用いて少なくとも摩擦接続的に結合されており、前記第1の接合材(130)は前記成形部分を少なくとも部分的に充填し、前記制御電極(100)と前記導電性層(115)とを接続する。

(もっと読む)

化合物半導体装置の製造方法、基板評価装置及び基板評価方法

【課題】化合物半導体層を形成する前の基板の状態で非接触のスクリーニングを行うことで、事前に化合物半導体層の不良発生を認識してこれを防止することができ、歩留まりの向上及び製造コストの削減を可能とする信頼性の高い化合物半導体装置を得る。

【解決手段】偏光レーザ12によりSiC基板1の基板面に偏光レーザ光を照射し、検出部13によりSiC基板1からの発光を検出し、表示部14によりSiC基板1の発光強度の面内分布を得て、SiC基板1の窒素混入量を評価した後、SiC基板1の上方に化合物半導体積層構造2を形成する。

(もっと読む)

半導体装置

【課題】結晶欠陥に起因したリーク電流を低くする。

【解決手段】ウェル106は、半導体基板100の表層に形成されており、第2導電型を有している。ドレイン拡散層130は、半導体基板100の表層に形成されており、ウェル106と接している。ドレイン拡散層130は、第1導電型を有する。ソース拡散層140はウェル106内に形成されており、第1導電型を有している。ゲート絶縁膜110は、半導体基板100半導体基板上に形成されており、平面視でドレイン拡散層130とソース拡散層140の間に位置している。ゲート電極120は、ゲート絶縁膜110上に形成されている。そして平面視で、半導体基板100は、結晶欠陥の密度が相対的に高い結晶欠陥集中領域101を有している。結晶欠陥集中領域101は、ウェル106と接していない。

(もっと読む)

半導体装置の製造方法

【課題】微細化に対応した半導体装置を提供する。

【解決手段】半導体基板の第1の領域内に第1の方向に沿って交互に配置されるように第1及び第2の素子分離領域を形成する。この際、第1及び第2の素子分離領域のうち少なくとも一方の素子分離領域の側面は半導体基板の主面に対して垂直とならないように第1及び第2の素子分離領域を形成する。この後、第1及び第2の素子分離領域の上部を除去して、第1の素子分離領域と第2の素子分離領域の間の半導体基板をフィンとして形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】低電流領域でのオン電圧を低減することができる、SiC−IGBTを備える半導体装置およびその製造方法を提供すること。

【解決手段】エミッタ電極26と、エミッタ電極26に接続されたエミッタ領域41と、エミッタ領域41に対してSiC半導体層23の裏面25側にエミッタ領域41に接して形成されたチャネル領域39と、チャネル領域39に対してSiC半導体層23の裏面25側にチャネル領域39に接して形成されたSiCベース層33と、SiCベース層33に対してSiC半導体層23の裏面25側にSiCベース層33に接して形成されたコレクタ領域37と、コレクタ領域37に接続されたコレクタ電極27とを含む、SiC−IGBT9に対してMOSFET11を並列に接続する。

(もっと読む)

半導体装置の製造方法

【課題】電極と半導体基板が良好にオーミック接合している半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の電極形成面に、単原子の金属イオンを注入するイオン注入工程と、金属イオンが注入された半導体基板をアニール処理して半導体基板にシリサイド層を形成するアニール工程と、アニール工程の後に、半導体基板の電極形成面に電極を形成する電極形成工程とを備えている。

(もっと読む)

31 - 40 / 8,588

[ Back to top ]