国際特許分類[H01L29/78]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | 絶縁ゲートによって生じる電界効果を有するもの (29,475)

国際特許分類[H01L29/78]の下位に属する分類

薄膜トランジスタ (12,139)

浮遊ゲートを有するもの (4,374)

電荷トラッピングゲート絶縁体,例.MNOSメモリトランジスタ,を有するもの (4,374)

国際特許分類[H01L29/78]に分類される特許

21 - 30 / 8,588

4h−SiC半導体素子及び半導体装置

【課題】 4h-SiC半導体素子のオン状態の抵抗低減とスイッチング速度向上実現する。

【解決手段】 (0001)面4h-SiC半導体素子のチャネル領域周囲に対してトレンチ溝を設け、シリコン酸化膜を埋め込む。トレンチ溝の酸化膜を、c軸方向へは引っ張り応力が加わり、c軸に垂直な平面上の二つ以上の軸からの圧縮応力が加わるように、平面レイアウトする。例えば、酸化膜で埋め込まれたトレンチ溝を、チャネルを囲む多角形としたり、離散的に配置する場合、チャネルを中心に対称的に配置するレイアウトでもよい。

(もっと読む)

半導体装置の製造方法

【課題】表面側保護膜が裏面側フォトレジストの剥離液に対する耐性を備えていなくても、表面側に保護膜を形成し裏面側Si基板にパターンエッチングして溝を形成した後、裏面側のフォトレジストだけを剥離することができるプロセス工程を有する半導体装置の製造方法の提供。

【解決手段】半導体基板1の表面側に半導体機能領域20を形成し、裏面側を研削して半導体基板1を所要の厚さに減じた後、表面側に保護膜24を塗布し、裏面側にフォトレジスト25を用いて所要の開口パターンを形成し、該パターン開口部から半導体基板1をエッチングして裏面に溝16を形成し、その後、裏面側のフォトレジスト25を研磨により除去し、裏面側半導体機能層を形成する半導体装置の製造方法とする。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】歩留まりを向上することができる炭化珪素半導体装置の製造方法を提供する。

【解決手段】炭化珪素半導体装置100の製造方法は以下の工程を有する。第1の主表面1との第2の主表面2とを有する炭化珪素基板80が準備される。第1の主表面1に電極が形成される。炭化珪素基板80は六方晶の結晶構造を有し、第1の主表面1の{0001}面に対するオフ角が±8°以内であり、第1の主表面1は、炭化珪素のバンドギャップ以上のエネルギーを有する励起光が照射された場合に、第1の主表面1に生ずる750nm以上の波長域における発光領域3の密度が1×104cm-2以下であるような特性を有する。

(もっと読む)

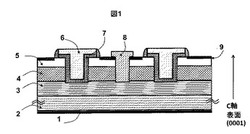

電界効果トランジスタ

【課題】耐圧および電流コラプス抑制性能をさらに向上できる電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタによれば、ゲート絶縁膜20を、ストイキオメトリなシリコン窒化膜よりもシリコンの比率が高いシリコン窒化膜で作製されたコラプス抑制膜18と上記コラプス抑制膜18上に形成されたSiO2絶縁膜17とを有する複層構造とすることにより、耐圧を向上できるだけでなく、電流コラプスも抑制できる。

(もっと読む)

電力用半導体装置およびその製造方法

【課題】フィールドプレート電極を有するトレンチゲート構造を備えた電力用半導体装置においてゲート−ソース間容量を低減する。

【解決手段】電力用半導体装置は、第1導電形の第1の半導体層2、フィールド絶縁膜6、フィールドプレート電極7、第1の絶縁膜8、導電体9、第2の絶縁膜11、ゲート絶縁膜10、及びゲート電極12を備える。フィールドプレート電極7は、フィールド絶縁膜6を介して第1の半導体層2のトレンチ5内に設けられる。第1の絶縁膜8は、フィールドプレート電極7上に設けられ、フィールド絶縁膜6とともにフィールドプレート電極7を取り囲む。導電体9は、第1の絶縁膜8上に設けられ、フィールドプレート電極7とは絶縁される。ゲート電極12は、フィールド絶縁膜6の上端上に設けられ第2の絶縁膜11を介して導電体に隣接し、ゲート絶縁膜10を介してトレンチ5内に設けられる。

(もっと読む)

半導体装置

【課題】ハイサイド素子として用いても誤動作が少なく、かつオン耐圧およびオフ耐圧の双方を高く維持することのできる半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBの内部には、p-エピタキシャル領域EP1が、その主表面側にはp-エピタキシャル領域EP2が、その主表面側にはn型ドリフト領域DRIとp型ボディ領域BOとが形成されている。p-エピタキシャル領域EP1とp-エピタキシャル領域EP2との間には、これらの領域を電気的に分離するためにn+埋め込み領域NBが形成されている。n+埋め込み領域NBとp-エピタキシャル領域EP2との間には、p-エピタキシャル領域EP2よりも高いp型不純物濃度を有するp+埋め込み領域PBが形成されている。p+埋め込み領域PBは、n型ドリフト領域DRIとp型ボディ領域BOとの接合部の少なくとも直下に位置し、かつn型ドリフト領域DRIと接するドレイン領域DRAの直下を避けて配置されている。

(もっと読む)

半導体装置およびその製造方法

【課題】トンネルFETのオン電流の劣化を抑制しつつ、オフ電流を低減することが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、溝が形成された基板と、前記基板上の前記溝に隣接する位置にゲート絶縁膜を介して形成され、前記溝の反対側に位置する第1側面と、前記溝側に位置する第2側面とを有するゲート電極とを備える。さらに、前記装置は、前記ゲート電極の前記第1側面に形成された第1の側壁絶縁膜と、前記ゲート電極の前記第2側面と前記溝の側面に形成された第2の側壁絶縁膜とを備える。さらに、前記装置は、前記基板内において、前記ゲート電極の前記第1側面に対し前記第1の側壁絶縁膜側に形成された、第1導電型のソース領域と、前記基板内において、前記ゲート電極の前記第2側面と前記溝の側面に対し前記第2の側壁絶縁膜側に形成された、第2導電型のドレイン領域とを備える。

(もっと読む)

半導体装置

【課題】低オン抵抗および高耐電圧を両立させることができ、デバイスサイズの小型化、製造歩留まりの向上およびコストの低減を達成することができる半導体装置を提供する。

【解決手段】基板5と、基板上5に形成され、ゲートトレンチ11が形成されたエピタキシャル層6と、ゲートトレンチ11の側面14および底面15に形成されたゲート絶縁膜17と、ゲートトレンチ11に埋め込まれ、ゲート絶縁膜17を介してエピタキシャル層6に対向しているゲート電極20と、エピタキシャル層6の表面側から裏面側へ向かって順に形成されたソース層25、チャネル層26およびドリフト層27とを含む半導体装置1において、オン抵抗Ronを変数yとし、耐電圧Vbを変数xとする関数で表したときに、下記関係式(1)を成立させる。

y≦9×10−7x2−0.0004x+0.7001…(1)

(もっと読む)

CMOS集積回路及び増幅回路

【課題】入力トランジスタの構造を櫛形構造にしてゲート抵抗を抑えつつ、NFの増大を防ぐことが可能なCMOS集積回路を提供する。

【解決手段】トランジスタは、ゲート配線から櫛歯状に延びて形成され、信号入力端子からの入力信号が供給されるゲート電極と、ゲート配線に対向した位置に形成されるソース配線から、ゲート電極の櫛歯の間に1つ起きに櫛歯状に延びて形成される、接地端子に接続されたソース電極と、ゲート配線に対向した位置に形成されるドレイン配線から、ゲート電極の櫛歯の間のソース電極が存在しない箇所に櫛歯状に延びて形成される、電源端子に接続されたドレイン電極と、を備え、ゲート電極と、ソース電極またはドレイン電極とは、重なり合う領域が存在しないことを特徴とする、CMOS集積回路が提供される。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】炭化珪素半導体装置に含まれる炭化珪素層の側面の面方位を特定の結晶面により近づけることができる炭化珪素半導体装置の製造方法を提供する。

【解決手段】基板1上に、主表面が設けられた炭化珪素層19が形成される。炭化珪素層19の主表面の一部を覆うマスク17が形成される。主表面に対して傾斜した側面SSが炭化珪素層19に設けられるように、マスク17が形成された炭化珪素層19の主表面に対して、塩素系ガスを用いた熱エッチングが行われる。熱エッチングを行う工程は、塩素系ガスの分圧が50%以下である雰囲気下で行われる。

(もっと読む)

21 - 30 / 8,588

[ Back to top ]