国際特許分類[H01L29/788]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | 絶縁ゲートによって生じる電界効果を有するもの (29,475) | 浮遊ゲートを有するもの (4,374)

国際特許分類[H01L29/788]に分類される特許

4,271 - 4,280 / 4,374

相補型不揮発性メモリ素子、その動作方法、その製造方法、及びそれを含む論理素子、並びに半導体装置とその読み込み動作回路

【課題】 相補型不揮発性メモリ素子、その動作方法、その製造方法、及びそれを含む論理素子、並びに半導体装置とその読み込み動作回路を提供する。

【解決手段】 第1不揮発性メモリ素子と、前記第1不揮発性メモリ素子上に積層された、第1不揮発性メモリ素子と相補的関係にある第2不揮発性メモリ素子とを含む相補型不揮発性メモリ素子であって、さらに、前記第1及び第2不揮発性メモリ素子の間にボンディング材が備えられた不揮発性メモリ素子である。

(もっと読む)

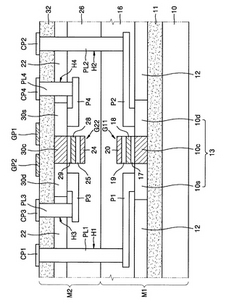

2つの制御領域を有する集積された電界効果トランジスタ、その使用、およびその製造方法

本発明は、特に、SOI技術およびサリサイド技術により、ダブルゲート・トランジスタ(10)として生成される、電界効果トランジスタ(10)に関する。トランジスタ(10)は、5ボルトよりも高いまたは9ボルトよりもさらに高いターンオン電圧に適し、非常に小さなチップ表面のみを必要とする。トランジスタ(10)は基板領域(14)を有する。基板領域(14)は、2つの電極領域(16、18)と、2つの電気的に絶縁性の絶縁層(100、102)であって、基板領域(14)の対向する面に配置され、制御領域(20、22)に隣接する、絶縁層と、少なくとも1つの電気的に絶縁性の領域(12、110)と、導電性の接続領域(28)、または、1つの電極領域(16)と該基板領域(14)との間の導電性の接続領域の部分(230)とに囲まれる。  (もっと読む)

(もっと読む)

スプリットゲート型のフラッシュメモリ素子及びその製造方法

【課題】 スプリットゲート型のフラッシュメモリ素子及びその製造方法を提供する。

【解決手段】 フローティングゲート及びコントロールゲートを形成する前に半導体基板上にマスクパターンを形成した後、マスクパターンの側壁によって自己整列されるようにフローティングゲート及びコントロールゲートを順次形成するスプリットゲート型のフラッシュメモリ素子。メモリセルを構成するフローティングゲートは、基板の主面に平行な第1面と、基板の主面に垂直である第2面と、第1面と第2面との間に延びているカーブ面を有する。コントロールゲートは、フローティングゲートの第1面の延長線とフローティングゲートの第2面の延長線との間で90゜より小さな角度範囲に限定される領域内で、前記フローティングゲートのカーブ面上に形成されている。

(もっと読む)

不揮発性メモリの一斉プログラミング

本発明の一実施形態は、ビットライン(図12のA又はB)に第1値を付加することと、第1値に基づいて第1状態を作成するために、ビットライン(図9のTr.566のドレイン)と共通の選択ライン(図9のTR.500のソース)とに対応したワードライン(図9のWLO又はWL31)をブーストすることと、ビットライン及び共通の選択ラインとに対応した特定の不揮発性記憶要素(例えば図9の518)に第1状態を維持するために、共通の選択ラインに対応した境界不揮発性記憶要素(例えば図9の532)をカットオフ状態にすることを備えている。ビットライン及び共通の選択ラインとに対応した別の不揮発性記憶要素(例えば図9の550)に第2状態を作成するために、ビットラインに第2値が付加され、ワードラインの少なくとも一部がブーストされる。この第2状態は第2値に基づくものである。第1状態と第2状態は時間的にオーバラップする。両方の不揮発性記憶要素は、それぞれ対応する状態に基づいて一斉にプログラムされる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】リーク電流を改善した高誘電率絶縁膜を電極間絶縁膜として使用する半導体装置及びその製造方法を提供することである。

【解決手段】半導体装置は、半導体基板上に形成された第1の絶縁膜と、前記第1の絶縁膜上に形成された第1のゲート電極と、前記第1のゲート電極の上方に形成された第2のゲート電極と、前記第1のゲート電極と第2のゲート電極との間に挟まれた結晶化した第2の絶縁膜を具備することを特徴とする。

(もっと読む)

不揮発性半導体メモリ装置およびその動作方法

【課題】電源電圧相当の電圧でメモリデバイスの閾値電圧を最大限に上昇させる動作を実現する。

【解決手段】半導体基板2とゲート電極6との間に形成され電荷蓄積能力を有する積層膜5を備えるメモリトランジスタ1は、書き込み時と読み出し時とで短チャネル効果が生じているか否かの境界として見積もられるチャネル長Lminが異なり、当該異なるチャネル長Lmin(R)とLmin(W)の間に、実デバイスのチャネル長Lを有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】 複数のスタックゲート型メモリセルを含むフラッシュメモリにおいて、消去前書込動作を不要とすることにより一括消去動作に要する時間を短縮し、データの書換動作に要する時間も短縮することである。

【解決手段】 消去時に、複数のメモリセルのソース1003からフローティングゲート1005に同時に電子を注入する。それにより、複数のメモリセルのしきい値電圧が上昇する。プログラム時に、選択されたメモリセルのフローティングゲート1005からドレイン1002に電子を放出する。それにより、選択されたメモリセルのしきい値電圧が下降する。

(もっと読む)

スプリットゲート型フラッシュメモリ素子及びその製造方法

【課題】ディスターバンス問題を防止できるスプリットゲート型フラッシュメモリ素子及びその製造方法を提供する。

【解決手段】バルクシリコン基板の活性領域に形成されているシリコンエピタキシャル層と、素子のソース及びドレイン間のバルクシリコン基板に形成されているディスターバンス防止用絶縁膜とを備えるスプリットゲート型フラッシュメモリ素子であり、該スプリットゲート型フラッシュメモリ素子では、ディスターバンス防止用絶縁膜は、STI形成工程を利用して形成される。

(もっと読む)

ビットライン短絡のないメモリ装置用ハードマスクプロセス

MirrorBit(トレードマーク)フラッシュメモリの製造方法は、半導体基板(102)を準備し(602)、電荷トラップ誘電体層(504)を堆積する(606)。第1及び第2のビットライン(512)が埋め込まれ(608)、ワードライン層(515)が堆積される(610)。ハードマスク層(516)はワードライン層(515)の上に堆積される(612)。ハードマスク層(516)は、電荷トラップ誘電体層(504)を破損することなく除去するため調製された材料からなる。フォトレジスト(518)はワードライン層(515)の上に堆積され、ハードマスク(519)を形成するため使用される(618)。フォトレジスト(518)は除去される(620)。ワードライン層(515)はワードライン(525−528)を形成するためハードマスク(519)を使用して処理される。  (もっと読む)

(もっと読む)

フラッシュッモリ素子の製造方法

【課題】ONO層のスマイリング現象及びトンネル酸化膜のバーズビーク現象を防止することができ、コントロールゲートの面抵抗の増加を抑制することができるうえ、全体時間時間を短縮して生産性を向上させることができるフラッシュメモリ素子の製造方法を提供する。

【解決手段】ゲート形成工程でセル領域及び周辺回路領域の半導体基板上にゲートを形成する段階と、前記ゲート形成工程時のエッチング損傷を回復するために第1急速熱酸化工程を行うことにより、サイドウォール酸化膜を形成する段階と、前記セル領域にセルトランジスタの接合部を形成する段階と、前記周辺回路領域に周辺回路トランジスタの接合部を形成する段階と、前記接合部に注入されたイオンを活性化させるために第2急速熱酸化工程を行う段階とを含む。

(もっと読む)

4,271 - 4,280 / 4,374

[ Back to top ]