国際特許分類[H01L29/788]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | 絶縁ゲートによって生じる電界効果を有するもの (29,475) | 浮遊ゲートを有するもの (4,374)

国際特許分類[H01L29/788]に分類される特許

4,301 - 4,310 / 4,374

トンネル層に量子ドットを有するトランジスタ

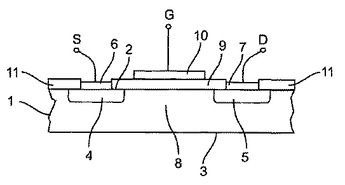

本発明は、半導体本体(1)内に配置された半導体部品を記述したもので、前記半導体部品は、第1の導電型である少なくとも1つのソース領域(4)及び少なくとも1つのドレイン領域(5)を有し、ソース領域とドレイン領域の間に配置された第2の導電型である少なくとも1つの本体領域(8)を有し、絶縁層(9)により半導体本体から絶縁された少なくとも1つのゲート電極(10)を有し、前記絶縁層(9)は好ましくは焼結された一体化量子ドット含有層である。本発明は更に、量子ドット含有誘電性懸濁液が半導体本体に塗布され、次に例えば焼結によって一体化される上記の半導体部品の作製方法を記述する。  (もっと読む)

(もっと読む)

VSS抵抗が低く、ドレイン誘起バリアハイト効果が低減されたフローティングゲートメモリセルの構造およびその製造方法

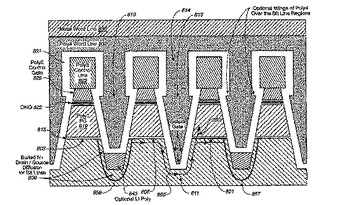

フローティングゲートメモリセル202は、基板204上に基板204中のチャネル領域222を覆う状態で配置されたスタックゲート構造208を有する。フローティングゲートメモリセル202は更に、基板204中にスタックゲート構造208に隣接して形成されたリセス228を有し、リセス228は側壁230、底部232、深さ236を有する。フローティングゲートメモリセル202は更に、リセス228の側壁230に隣接し、且つ、スタックゲート構造208の下に配置されるソース234を有する。フローティングゲートメモリセル202は更に、リセス228の底部232にあり、ソース234の下に配置されるVss接続領域238を有し、Vss接続領域238はソース234に接続されている。Vss接続領域238はリセス228の底部232の下に配置されているため、チャネル領域222におけるソース234の側方拡散が低減されている。  (もっと読む)

(もっと読む)

High−K材料とゲート間プログラミングとを使用する不揮発性メモリ・セル

不揮発性メモリ・デバイスは、ソース/ドレイン領域の間のチャネル領域と、フローティング・ゲートと、制御ゲートと、チャネル領域とフローティング・ゲートとの間の第1の誘電体領域と、フローティング・ゲートと制御ゲートとの間の第2の誘電体領域とを有する。第1の誘電体領域はHigh−K材料を含む。不揮発性メモリ・デバイスは、フローティング・ゲートと制御ゲートとの間で第2の誘電体領域を介して電荷を移動させることによってプログラムおよび/または消去される。 (もっと読む)

パッド下に素子を備える手法によるウェハの有効利用

半導体構造(20)のパッドエリア(21)下に能動素子(25)を組み込むことにより、シリコンエリアのより効率的な利用を可能とする。パッドエリア(21)は、上方に第1の金属層(23)を備えた基板(22)を含む。第2の金属層(26)は第1の金属層(23)の下とする。能動素子(25)は基板内であって、第2の金属層(26)の下に備えられる。誘導体層(24)は第1の金属層(26)と第2の金属層(23)とを分離する。誘導体層(24)内のビア(27)は第1の金属層(23)と第2の金属層(26)とを電気的に接続する。ビア(27)は能動素子(25)と接続する。隣接金属層(424、425、426)を第1の金属層(23)と第2の金属層(26)の間に配置してもよい。  (もっと読む)

(もっと読む)

ピラー構造セルのフラッシュメモリ技術

ピラー形不揮発性メモリセル803は各々がトレンチ810によって隣接するメモリセルから絶縁されるメモリセルを各々有している。各メモリセルは基板上に処理層を積層することによって形成される。すなわち、トンネル酸化物層815、ポリシリコンフローティングゲート層819、ONOまたは酸化物層822、ポリシリコンコントロールゲート層825である。ステップの多くの態様が自己整合される。これらのメモリセルのアレイにはより少ない分割しか必要ない。さらに、このメモリセルは、電子がフローティングゲート819に対して直角またはほぼ垂直843に向けられるので、プログラミング特性が増強される。  (もっと読む)

(もっと読む)

フラッシュメモリデバイス

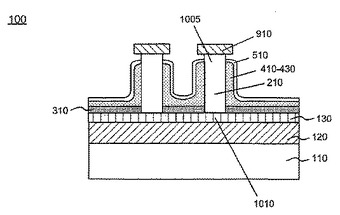

メモリデバイス(100)は、導電構造(210)、複数の誘電層(410−430)、及び、制御ゲート(510)を含む。誘電層(410−430)は導電構造(210)の周りに形成され、制御ゲート(510)は誘電層(410−430)上に形成される。導電構造(210)の一部はメモリデバイス(100)のドレイン領域(1005)として機能し、また、誘電層(410−430)の少なくとも1つは、メモリデバイス(100)の電荷蓄積構造として機能する。誘電層(410−430)は、酸化物−窒化物−酸化物層を含む。  (もっと読む)

(もっと読む)

ブリッジ電界効果トランジスタメモリセル、上記セルを備えるデバイス、および、ブリッジ電界効果トランジスタメモリセルの製造方法

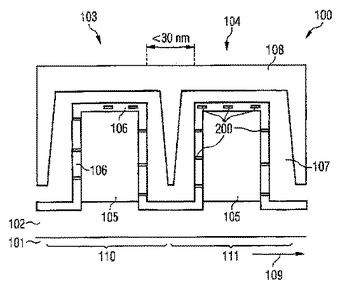

本発明は、第1および第2の各ソース/ドレイン領域、第1および第2の各ソース/ドレイン領域の間に配置されたチャネル領域とを備え、これらの各ソース/ドレイン領域とチャネル領域とが半導体ブリッジに形成されている、ブリッジ電界効果トランジスタメモリセルに関するものである。

本発明のメモリセルは、さらに、半導体ブリッジの少なくとも部分上に堆積されている電荷記憶層と、電荷記憶層の少なくとも一部上の金属性で導電性のゲート領域とを備え、電荷記憶層は、ブリッジ電界効果トランジスタメモリセルに所定の電気的電圧を印加することにより、選択的に、電気的な電荷キャリアが、電荷記憶層に対し導入されるように、または、電荷記憶層から除去されるように配置されている。  (もっと読む)

(もっと読む)

高K誘電体膜

誘電体層(14,22,24,32)は、ランタン、ルテチウム、及び酸素により構成され、かつ2つの導体の間、または導体(14,20,34)と基板(12,26,30)との間に形成される。一の実施形態では、誘電体層は基板を覆って形成され、境界層を追加する必要がない。別の実施形態では、誘電体層(22,42,46)に含まれる元素の分布は、ランタン含有量またはルテチウム含有量に関して傾斜する、または誘電体層(22,42,46)は別の構成として、アルミニウムを含むことができる。更に別の実施形態では、絶縁層を導体または基板と誘電体層との間、または導体及び基板の両方と誘電体層との間に形成する。誘電体層は、分子ビームエピタキシー法によって形成することが好ましいが、原子層化学気相成長、物理気相成長、有機金属化学気相成長、またはパルスレーザ堆積によって形成することもできる。  (もっと読む)

(もっと読む)

縦型スプリットゲートNROMメモリ装置及びその形成方法

【課題】NROMセルの利点と縦型メモリセルの利点とを備えるメモリデバイスを提供する。

【解決手段】スプリットゲート縦型NROMメモリセル(1890)は、複数の酸化物柱状体(1830、1831)から構成される。複数の酸化物柱状体の各々の上部にはソース/ドレイン領域(1840、1841)が形成される。溝部が、酸化物柱状体の各対の間に形成される。ポリシリコン制御ゲート(1800)が、酸化物柱状体の対の間の溝部に形成される。ポリシリコンプログラムゲート(1805、1806)が、制御ゲートと各酸化物柱状体との間に形成される。プログラムゲートは、各酸化物柱状体の側壁に沿って延在する。ゲート絶縁層(1802、1803)が、各プログラムゲートとその近傍の酸化物柱状体との間に形成される。各ゲート絶縁層は、少なくともひとつの電荷を捕獲する電荷捕獲構造を有する。一実施形態において、ゲート絶縁構造は、酸化物−窒化物−酸化物の層である。中間絶縁層(1822、1824)が、プログラムゲートと制御ゲートとの間に形成される。

(もっと読む)

極薄シリコンにおけるNROM型フラッシュメモリデバイス

【課題】SOI技術を取り入れたCMOSデバイスにおける浮遊ボディの影響を抑制可能とする。

【解決手段】極薄シリコン・オン・インシュレータ構造においてNROMフラッシュメモリセルを実現する。平面型デバイスでは、ソース/ドレイン領域間のチャネルが通常時に完全空乏化されている。ソース/ドレイン領域と上方のゲート絶縁層との間に酸化物層を形成することで絶縁層を設ける。制御ゲートがゲート絶縁層の上部に形成される。縦型デバイスでは、ソース/ドレイン領域に側面が接する酸化物柱状体を基板から延伸させる。エピタキシャル再成長により、酸化物柱状体の側面に沿って極薄シリコンボディ領域が形成される。本構造の上部には、第2のソース/ドレイン領域が形成される。さらにその上部にゲート絶縁層及び制御ゲートが形成される。

(もっと読む)

4,301 - 4,310 / 4,374

[ Back to top ]