国際特許分類[H01L29/788]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | 絶縁ゲートによって生じる電界効果を有するもの (29,475) | 浮遊ゲートを有するもの (4,374)

国際特許分類[H01L29/788]に分類される特許

4,331 - 4,340 / 4,374

不揮発性メモリおよびその製造方法

トランジスタの制御ゲート(28)およびウェル領域(12)に、それぞれ、第1および第2の電圧を印加するステップを含む不揮発性メモリのトランジスタ(10)の電荷蓄積場所から放電するための方法。第1の電圧はトランジスタの制御ゲートに印加され、制御ゲートは、トランジスタの選択ゲート(18)に隣接して位置する一部を少なくとも有する。トランジスタは、制御ゲートの下に位置するトランジスタの構造の誘電体(22,26)内に配置されたナノクラスタ(24)を有する電荷蓄積場所を含む。最後に、第2の電圧が、制御ゲートの下に位置するウェル領域(12)に印加される。第1の電圧および第2の電圧の印加により、電荷蓄積場所のナノクラスタから電子を放出するために前記構造の両端に電圧差が発生する。  (もっと読む)

(もっと読む)

UVチャージングを減少するPECVDシリコンリッチ・シリコン酸化物層

メタライゼーションの前に、UV透過を低減するシリコンリッチ・シリコン酸化物層(500)をPECVDにより層間絶縁膜(300)上にたい積する。これによりVtが減少する。実施形態は、1.7から2.0のR.I.を有するUVを透過しないシリコンリッチ・シリコン酸化物層(500)をたい積するステップを含んでいる。  (もっと読む)

(もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

電気試験データに基づいてゲート絶縁層の特性および特徴を制御するための方法、これを実施するためのシステム

本発明は、一般に、電気試験データ(46)に基づいてゲート絶縁層(16)の特性および特徴を制御する各種方法、ならびにこれを実施するためのシステムを対象としている。例示的な一実施形態では、上記方法は、少なくとも1つの半導体デバイスに少なくとも1つの電気試験を実施するステップと、以降形成する半導体デバイスに少なくとも1つのゲート絶縁層(16)を形成するために実施する少なくとも1つのプロセス操作の少なくとも1つのパラメータを、電気試験から得られた電気データに基づいて決定するステップと、決定されたパラメータを含む少なくとも1つのプロセス操作を実施して、ゲート絶縁層(16)を形成するステップとを有する。  (もっと読む)

(もっと読む)

電界効果トランジスタ及びその製造方法

SiC基板1と、SiC基板1表面に形成されたソース3a及びドレイン3bと、SiC表面に接して形成され厚さが1分子層以上のAlN層5と、その上に形成されたSiO2層とを有する絶縁構造と、この絶縁構造上に形成されたゲート電極15とを有しており、SiCとの間の界面状態を良好に保ちつつ、リーク電流を抑制することができる。 (もっと読む)

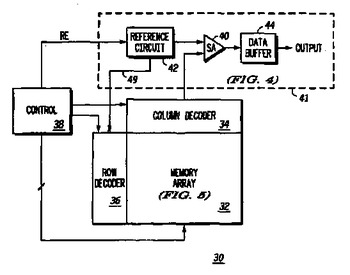

不揮発性メモリにおける基準トランジスタ用可変ゲート・バイアス

不揮発性メモリ(30)はナノクリスタルメモリセル(50、51、53)を備える。メモリセルトランジスタ(50、51、53)のプログラム及び消去閾値電圧は、プログラム/消去動作の回数の関数として上昇する。読み出し動作の間、基準トランジスタ(46)がセル電流と比較するための基準電流を供給する。基準トランジスタ(46)がナノクリスタルを含まないことを除いて、基準トランジスタ(46)は、メモリセルトランジスタ(50、51、53)を製造する際に用いるのと同様のプロセスで製造される。同様のプロセスを用いて基準トランジスタ(46)及びメモリセルトランジスタ(50、51、53)双方を製造することにより、基準トランジスタ(46)の閾値電圧は、メモリセルトランジスタ(50、51、53)の閾値電圧のずれに追従する。基準トランジスタ(46)のゲートにバイアスをかけるために、読み出し制御回路(42)が設けられている。読み出し制御回路(42)は、基準トランジスタ(46)のドレイン電流を検知し、基準電流をセル電流に対して実質的に一定値に維持するように、ゲートバイアス電圧を調節する。  (もっと読む)

(もっと読む)

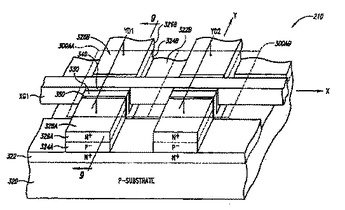

耐久性が改善された分離トランジスタメモリ及びその製造方法

本発明は、フラッシュメモリ装置のような不揮発性メモリ装置に使用されるフローティングゲートトランジスタ構造を有する。1つの実施の形態において、システムはCPUとメモリ装置とを有し、該メモリ装置は複数のメモリセルを有するアレイを具備する。メモリセルは複数の柱状構造とこれら柱状構造間に挿入され、これら柱状構造のうちの1つに近接するフローティングゲート構造とを有する。他の実施の形態において、メモリ装置10は、複数のメモリセルを有するアレイを具備する。メモリセルは隣接する複数のFETを有し、これらFETは、ソース/ドレイン領域と共通のフローティングゲート構造を有し、該フローティングゲート構造は、1つのFETのソース/ドレイン領域から第1間隔だけ離間し、且つ、他のFETのソース/ドレイン領域から第2間隔だけ離間している。さらに他の実施の形態において、メモリ装置は、基板上に複数の柱状構造を配置し、これら複数の柱状構造間にフローティングゲートを、これら柱状構造のうちの1つに近接するように挿入することによって形成される。  (もっと読む)

(もっと読む)

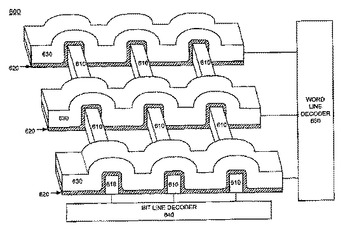

垂直方向の突起部を有するフローティングゲート構造

基板面から離れて延在する突起部を有するフローティングゲート構造を開示する。この突起部によって、フローティングゲートとコントロールゲートとを結合するための増加した表面積をフローティングゲートに提供することが可能となる。1つの実施形態では、フローティングゲートの個々の側面でワードラインが下方へ延在して、同じ列の隣接するフローティングゲートを遮蔽する。別の実施形態では、突起部を有するフローティングゲートの組立て製造処理工程を開示する。残りのフローティングゲートに対して自己位置合せを行うために突起部を形成してもよい。  (もっと読む)

(もっと読む)

不揮発性メモリのソース制御操作

フラッシュEEPROMなどの不揮発性メモリが、自己限定プログラミング技術を用いて並列にプログラムされ得るメモリセルを有する。個々のセルは、自己限定的に熱い電子で荷電され得る電荷記憶装置を有する。電荷記憶装置が必要なレベルの電荷に達すると、熱い電子はそれ以上生成されないか、或いは少数しか生成されない。熱い電子の生成が停止する電荷レベルは、セルに印加される電圧によって決まる。このように、複数のセルが並列にプログラムされ、印加電圧に対応する電荷レベルで各々のセルが自己限定される。  (もっと読む)

(もっと読む)

不揮発性メモリデバイス

不揮発性メモリデバイス(100)は、基板(110)、絶縁層(120)、フィン(210)、複数の誘電層(310〜330)及び制御ゲート(510/520)を備える。絶縁層(120)は、基板(110)上に形成され、フィン(210)は、絶縁層(120)上に形成される。誘電層(310〜330)は、このフィン(210)を覆うように形成され、制御ゲート(510/520)は、誘電層(310〜330)上に形成される。誘電層(310〜330)は、メモリデバイス(100)の電荷格納構造として機能する酸化物−窒化物−酸化物層を備える。  (もっと読む)

(もっと読む)

4,331 - 4,340 / 4,374

[ Back to top ]