国際特許分類[H01L29/788]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | 絶縁ゲートによって生じる電界効果を有するもの (29,475) | 浮遊ゲートを有するもの (4,374)

国際特許分類[H01L29/788]に分類される特許

4,291 - 4,300 / 4,374

非揮発性メモリの可変プログラミング

システムと方法は、様々な実施形態に従って非揮発性半導体メモリのプログラム妨害を抑制することを提供する。一実施形態では、NANDストリングの最後のワードラインに接続されているもの等のような選択メモリセルが、他のセル又はワードラインをプログラムするために利用される対応レベルと異なる一又は複数のプログラムベリファイレベル又は電圧を利用してプログラムされる。一実施形態は、プログラムオペレーションの間にストリングのためにプログラムされるべき最後のワードラインをプログラミングする際に、選択シジカル状態のためにより低い閾電圧ベリファイレベルを利用することを含む。他の実施形態は、選択シジカル状態に最後のワードラインのメモリセルをプログラムするために、より低いプログラム電圧を供給することを含む。いくつかの実施例においてより低いベリファイレベルを利用してプログラムされた状態を読み込むために、追加の読み込みレベルが設けられる。一実施形態では、NANDストリングのためにプログラムされるべき最後のワードラインのような選択メモリセル又はワードラインをプログラミングする際に、通常のステップサイズより大きい第2プログラム電圧ステップサイズが利用される。  (もっと読む)

(もっと読む)

重合体中のナノ結晶体を用いるフラッシュメモリ装置

【課題】本発明は、重合体薄膜中に自発形成された金属又は金属酸化物のナノ結晶体を用いた高効率かつ低費用のナノフローティングゲートを有する、フラッシュメモリ素子及びその製造方法に関する

【解決手段】

本発明は、従来のフラッシュメモリ素子のナノ結晶体の形成過程と比較し非常に簡便にナノ結晶体を形成することを可能にする。全体的に均一な分布を有する結晶体であるため、重合体層中に結晶体の凝集現象を伴わずにナノ結晶体の大きさや密度を制御することが可能となる。更に本発明は、従来のナノフローティングゲートと比較し電気的または化学的に安全性を有するナノフローティングゲートを用いることにより、高効率かつ低費用のナノフローティングゲートを有するメモリ素子及びその製造方法を提供する。

(もっと読む)

ナノ対応可能なメモリデバイスおよび異方性電荷運搬アレイ

ナノ対応可能なメモリデバイスおよび異方性電荷運搬アレイ用の方法および装置が、記載される。一局面において、メモリデバイスは、基板と、基板のソース領域と、基板のドレイン領域とを含む。ナノエレメントの集団が、基板上のチャネル領域より上に堆積される。このナノエレメントの集団は、一実施形態において、金属量子ドットを含む。トンネル誘電体層が、チャネル領域の上に横たわる基板上に形成され、金属マイグレーションバリア層が、誘電体層全体にわたって堆積される。ゲートコンタクトは、ナノエレメントの薄膜全体にわたって形成される。ナノエレメントは、横への電荷移動を低減できる。メモリデバイスは、シングルステートまたはマルチステートのメモリデバイスであり得る。複数の離散的なエネルギレベルを有する1つ以上の量子ドットまたは分子を備えるマルチステートメモリデバイスにおいて、そのデバイスを充放電する方法が開示される。  (もっと読む)

(もっと読む)

電荷を非対称に捕獲する多値メモリセル

【課題】高メモリ密度、低電力消費、及び高信頼性を達成可能なNAND型多値メモリセルを提供する。

【解決手段】NAND型多値メモリセルは、2つのドレイン/ソース領域を基板に有する。2つのドレイン/ソース領域の間における基板の上方には、酸化物−窒化物−酸化物構造体が形成される。このうち窒化物層は、電荷を非対称に捕獲する層として機能する。酸化物−窒化物−酸化物構造体の上方には、制御ゲートが配置される。ドレイン/ソース領域に非対称のバイアスをかけることで、ドレイン/ソース領域に高い電圧が生じ、これによってドレイン/ソース領域の略近傍における電荷捕獲層にGIDL(ゲートに起因するドレインでの電流漏れ)正孔注入処理を行い、正孔を非対称な分布で注入する。

(もっと読む)

縦型EEPROMNROMメモリデバイス

【課題】電荷捕獲領域の重なりがなく、過消去特性が改善された、より狭い素子間隔の高密度なNROMメモリアレイを製造する方法及び構造体を提供する。

【解決手段】NOR又はNAND型高密度メモリ構成において縦型NROMメモリセル及び縦型選択ゲートを有効に利用するNROM EEPROMメモリデバイス及びアレイが開示される。本発明に係るメモリの実施形態では、縦型選択ゲート及び縦型NROMメモリセルを用いて、NOR及びNAND型NROM構成のメモリセル列、メモリセグメント及びメモリアレイを形成する。これらNROMメモリセル構成によって、構成要素として選択ゲートを有するメモリデバイス又はメモリアレイをより高密度にすることが可能となる。これらメモリデバイス又はメモリアレイにおいては、半導体製造プロセスによって作製可能な加工寸法を利用することができ、かつ、典型的なマルチビットNROMセルにおいて存在する電荷分離に関する問題を被ることがない。さらに、上述のメモリセル構造体は、NROMメモリセルからそれらに関連したビット/データ線及び/又はソース線とを絶縁する選択ゲートの後ろに、NROMメモリセルを配置することによって、擾乱及び過消去問題を軽減することが可能となる。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】シリコン基板にダメージを与えることなく、ウェットエッチングにより剥離することなく、小さい径のトンネル窓を形成できる不揮発性半導体記憶装置の製造方法の提供。

【解決手段】第1に反射防止膜7を介してKrF線レジスト8を塗布する。これによりレジストの開口寸法自体を小さくすると共に密着性を向上させてウェットエッチング中の剥離を防止する。第2に反射防止膜7のドライエッチングの際に第1の絶縁膜2の途中でエッチングを止める。これにより反射防止膜7を除去すると共に第1の絶縁膜2をドライエッチングにより薄膜化することによってその後のウェットエッチングの時間を短くして基板面方向への広がりを抑制する。第3に第1の絶縁膜2をウェットエッチングにより除去する。これによりシリコン基板1にプラズマダメージが入ることがなくなり、トンネル絶縁膜の信頼性を向上させる。

(もっと読む)

浮遊ゲート間のクロスカップリングを制限するシールド板

不揮発性記憶素子のセットを含むメモリシステムが開示されている。前記不揮発性記憶素子の各々は基板内のチャネルの両側のソース/ドレイン領域と、チャネルの上方の浮遊ゲートスタックとを含む。またメモリシステムは、隣接する浮遊ゲートスタック間に位置するとともにソース/ドレイン領域に電気的に接続されて隣接する浮遊ゲート間のカップリングを低減するシールド板のセットも含む。シールド板は不活性領域上に成長せずに、メモリの活性領域上に選択的に成長する。一実施形態では、シールド板はソース/ドレイン領域上に位置するエピタキシャル成長のシリコンである。 (もっと読む)

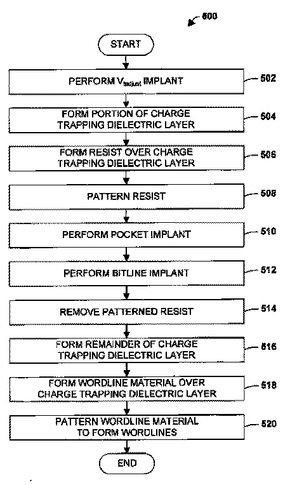

SONOSメモリセルの相補ビット妨害および蓄電の改善のためのポケット注入

デュアルビットメモリコアのアレイの少なくとも一部を形成する方法が開示される。最初に、電荷トラップ誘電層(608)の一部が基板(602)上に形成され、電荷トラップ誘電層(608)の一部の上にレジスト(614)が形成される。レジスト(614)がパターニングされ、ポケット注入(630)が所定の角度で実行され、基板(602)内にポケット注入部(620)が形成される。次に、基板(602)内に埋込みビット線(640)を形成するためにビット線注入(634)が実行される。次に、パターニングされたレジストが除去され、電荷トラップ誘電層(608)の残部が形成される。電荷トラップ誘電層の残部の上にワード線の材料(660)が形成されて、それはビット線(640)上にワード線(662)を形成するためにパターニングされる。ポケット注入部(620)は、特に、微細化によって生じるおそれのある相補ビット妨害(CBD)を軽減するのに役立つ。このように、ここに記載する発明思想により、半導体デバイスを小型化でき、高い実装密度を実現することができる。  (もっと読む)

(もっと読む)

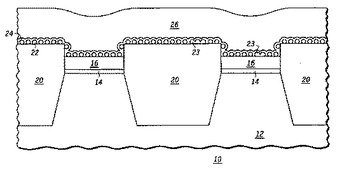

改良された表面形状を用いるメモリ構造の形成方法及びその構造。

半導体装置10のゲートカップリング比を増大させるため、超微細結晶等の個別素子22が浮遊ゲート16上に析出される。一実施形態において、個別素子22は、蒸気相中で予め形成され、静電気力によって半導体装置10に吸着される。一実施形態において、個別素子22は、それらが吸着されるチャンバとは異なるチャンバ内で予め形成される。更に別の実施例において、同じチャンバが全ての析出工程に使用される。界面層17は、必要に応じて、浮遊ゲート16と個別素子22との間に形成される。  (もっと読む)

(もっと読む)

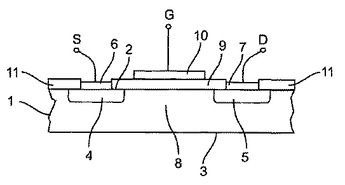

トンネル層に量子ドットを有するトランジスタ

本発明は、半導体本体(1)内に配置された半導体部品を記述したもので、前記半導体部品は、第1の導電型である少なくとも1つのソース領域(4)及び少なくとも1つのドレイン領域(5)を有し、ソース領域とドレイン領域の間に配置された第2の導電型である少なくとも1つの本体領域(8)を有し、絶縁層(9)により半導体本体から絶縁された少なくとも1つのゲート電極(10)を有し、前記絶縁層(9)は好ましくは焼結された一体化量子ドット含有層である。本発明は更に、量子ドット含有誘電性懸濁液が半導体本体に塗布され、次に例えば焼結によって一体化される上記の半導体部品の作製方法を記述する。  (もっと読む)

(もっと読む)

4,291 - 4,300 / 4,374

[ Back to top ]