国際特許分類[H01L29/788]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | 絶縁ゲートによって生じる電界効果を有するもの (29,475) | 浮遊ゲートを有するもの (4,374)

国際特許分類[H01L29/788]に分類される特許

4,311 - 4,320 / 4,374

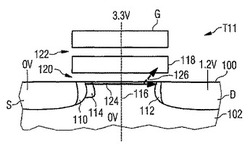

非対称のポケットドープ領域を有するメモリトランジスタおよびメモリユニット

本発明は、特に、ソース領域(S)近傍において、ポケットドープ領域(114)を1つ有しているフラッシュメモリトランジスタ(T11)に関する。上記メモリトランジスタ(T11)は、読み出し処理中において、ロードメモリ状態を妨害することなく機能する。 (もっと読む)

自己整合型電荷分離構造NROMフラッシュメモリ

【課題】電荷捕獲領域が重ならずにセルを小さくすることが可能なトランジスタを提供する。

【解決手段】窒化物リードオンリーメモリ(NROM)セルは、窒化物層を有し、前記窒化物層は、トランジスタの中心部の下方に配置されない。前記窒化物層を有するゲート絶縁層は、2つの部分を有する。各部分は、構造分離された(structurally defined and separated)電荷捕獲領域を有する。電荷は、トランジスタの動作方向に応じて、ある特定の捕獲領域に蓄積される。前記ゲート絶縁層の前記2つの部分は、ポリシリコンゲート構造体の中間部分から外側部分を分離する。

(もっと読む)

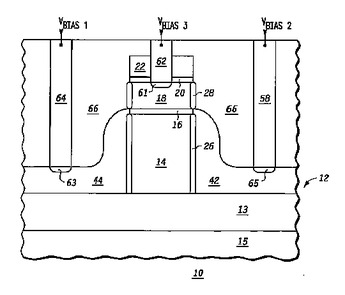

3つの電気絶縁電極を有するトランジスタ及びトランジスタの形成方法

トランジスタ(10)は別々に制御することができるゲート(44,42,18)を有するように形成される。3つのゲート領域は異なる電位でバイアスすることができ、かつこれらのゲート領域は異なる伝導特性を持つことができる。チャネルサイドウォール上の誘電体はチャネル上部の上の誘電体と異ならせることができる。ソース、ドレイン、及び3つのゲートとの電気コンタクトは別々に取る。ナノクラスター(143,144)のような電荷蓄積層をトランジスタのチャネルに隣接するように設け、そして電荷蓄積層を3つのゲート領域を通して制御することにより、揮発性メモリセル及び不揮発性メモリセルの両方を同じプロセスを使用して実現することにより世界共通のメモリプロセスを提供する。揮発性セルとして用いる場合、トランジスタの高さ、及びチャネルサイドウォール誘電体の特性によって記憶保持特性を制御する。不揮発性セルとして用いる場合、トランジスタの幅、及びチャネルを覆う誘電体の特性によって記憶保持特性を制御する。  (もっと読む)

(もっと読む)

ゲートによるジャンクションリーク電流を使用してフラッシュメモリをプログラミングする技術

メモリ素子をプログラムする方法と、ゲートによる接合リーク電流を利用してプログラムされたメモリ素子を提供する。本素子は、基板上のフローティングゲートと、基板内の活性領域と、フローティングゲートに隣接する第2ゲートを少なくとも含むことができる。本方法は、第1ゲートにバイアスをか印加することによってフローティングゲートの下の基板内に反転領域を生成する工程と、第2ゲートの付近に臨界電界を生成する工程を含むことができる。臨界電界を生成する工程は、活性領域に第1ポジティブバイアスを印加する工程と、第2ゲートに第1ポジティブバイアスより小さいバイアスを印加する工程を含むことができる。本素子は、活性領域に印加されるゼロボルトより大きい第1バイアスと、第2ゲートに印加される第1バイアスより大きい第2バイアスをさらに含む。第1バイアスと第3バイアスは、フローティングゲートと選択ゲートの間において基板内にリーク電流を生成するために選択される。  (もっと読む)

(もっと読む)

部分的シリサイド化シリコン層を有する集積回路

この集積回路(1)は、シリサイド化部(122)及び非シリサイド化部(123)を有する第1のシリコン層(120)を有する抵抗素子などの電気的装置(2)と、例えばキャパシタ、電界効果トランジスタ又は不揮発性メモリゲート堆積部などの他の電気的装置(3)とを有する。他の電気的装置(3)は、誘電層厚さ(D)を有する誘電層(130)を有する。電気的装置(2)の非シリサイド化部(123)は、誘電層厚さ(D)を有する他の誘電層(131)により被覆され、シリサイド化部(122)は、他の誘電層(131)により被覆されない。このような集積回路(1)は、リソグラフィ工程数の少ない本発明による方法によって形成可能となる。

(もっと読む)

(もっと読む)

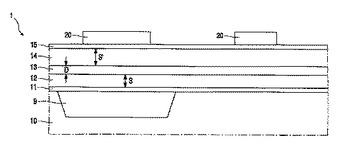

半導体装置と半導体装置の製造方法

バリア性を有する絶縁膜サイドウォールスペーサを有する半導体装置を提供する。 半導体装置は、半導体基板の上に形成されたゲート酸化膜とゲート電極と;半導体基板内に形成されたソース/ドレイン領域と;ゲート電極側壁上に形成された2層以上の積層サイドウォールスペーサであって、最外層以外の層として窒化膜を含み、最外層は、酸化膜又は酸化窒化膜で形成され、下面が半導体基板またはゲート酸化膜、又は窒化膜以外の他のサイドウォールスペーサ層と接している第1積層サイドウォールスペーサと;を有する。さらに、不揮発性メモリの積層ゲート電極構造と;積層ゲート電極構造の側壁上に形成され、中間層として半導体基板に接しない窒化膜を含む3層以上の第2積層サイドウォールスペーサと;を有することもできる。  (もっと読む)

(もっと読む)

過剰消去されたセルを復旧させるために、正のゲートストレスを使用したメモリデバイスおよびそのための方法

複数のメモリセルから構成されたフラッシュ電気的消去可能読出し専用メモリ(EEPROM)デバイス(10)の消去方法は、複数のメモリセル(10)をプリプログラミングするステップ(100)と、複数のメモリセル(10)に消去パルスを印加するステップ(110)と、を有し、これに消去検証(120)が続く。この消去検証(120)の後に、スレッショルド電圧が所定の最小レベル(VTMIN)を下回るメモリセルのソフトプログラミング(135)と、複数のメモリセル(10)への正のゲートストレスの印加(130)が続く。この消去方法は、過剰消去を防止し、スレッショルド電圧分布を低減する。  (もっと読む)

(もっと読む)

短チャネル効果を減少させる埋め込みチャネルフラッシュ構造

短チャネル効果を減少させたメモリセルを記載する。ソース領域(54)およびドレイン領域(56)を半導体ウェーハ(58)中に形成する。ソース領域(54)およびドレイン領域(58)の間にトレンチ領域(59)を形成する。このトレンチ領域、ソース領域およびドレイン領域の下に埋め込みチャネル領域(52)を形成する。半導体基板のトレンチ領域中にゲート絶縁層(60)を形成する。このゲート絶縁層は、埋め込みチャネル領域上に、およびソース領域とドレイン領域との間に形成される。埋め込みチャネル領域の上の半導体基板上に、制御ゲート層(70)を形成する。この制御ゲート層は、ゲート絶縁層によって埋め込みチャネルから分離される。  (もっと読む)

(もっと読む)

完全空乏型シリコン・オン・インシュレータのCMOSロジック

【課題】SOI技術を用いた部分空乏型CMOSデバイスにおける浮遊ボディの不必要な影響を制御可能とする。

【解決手段】シリコン・オン・インシュレータのCMOSメモリデバイスにおいて、引き出し線を含む領域が用いられる。引き出し線を逆方向にバイアスすることで、部分空乏型メモリセルのボディ領域から少数キャリアを取り除く。これにより、ボディ領域を完全空乏化し、浮遊ボディの不必要な影響を抑制する。

(もっと読む)

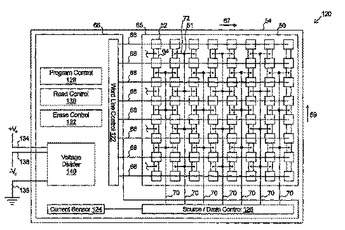

スタガー式ローカル接続構造を持つメモリセルアレイ

メモリセルアレイ(50)は、半導体基板(54)に製造された、2次元アレイのメモリセル(52)を含む。メモリセル(52)は、行方向(67)を形成する複数の行と、列方向(69)を形成する複数の列で並べられている。メモリセル(52)の各列は、複数の交互に配置されたチャネル領域(58)及びソース/ドレイン領域(64)を含む。各ソース/ドレイン領域(64)上には導電性インターコネクト(72)が配置されており、この導電性インターコネクト(72)はただ1つのその他のソース/ドレイン領域(64)に結合する。この1つのソース/ドレイン領域(64)とは、その列に隣接する第2の列に存在する領域である。導電性インターコネクト(64)は、1つおきの導電性インターコネクト(64)がその列の右側に隣接する列に接続するように、また、1つおきの導電性インターコネクトが、その列の左側に隣接する列に接続するように、配置される。複数のソース/ドレインコントロールライン(70)は、隣接するメモリセル(52)の列間に延在し、また、その隣接する列と列との間を結合する各導電性インターコネクト(72)に電気的に結合する。  (もっと読む)

(もっと読む)

4,311 - 4,320 / 4,374

[ Back to top ]