国際特許分類[H01L29/788]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | 絶縁ゲートによって生じる電界効果を有するもの (29,475) | 浮遊ゲートを有するもの (4,374)

国際特許分類[H01L29/788]に分類される特許

4,321 - 4,330 / 4,374

不揮発性メモリデバイス

選択的な横方向の電導率を有する活性層を含むことができるメモリデバイスである。活性層は複数のナノ粒子を含む。 (もっと読む)

ナノクラスターを備えた半導体デバイス

ナノクラスターを備えたデバイスを形成するプロセス。本プロセスは、ナノクラスター(例えばシリコンナノ結晶)を形成する段階と、デバイスの誘電体を形成する次の段階中に酸化剤によるナノクラスターの酸化を抑制するためにナノクラスターを覆って酸化バリア層を形成する段階とを含む。酸化バリア層の少なくとも一部は、誘電体の形成後に除去される。1つの実施例では、本デバイスは、ナノクラスターがメモリの電荷蓄積トランジスタの電荷蓄積位置として利用されるメモリである。この実施例では、酸化バリア層が、メモリの高電圧トランジスタ用のゲート誘電体を形成することにより、ナノクラスターを酸化剤から保護する。 (もっと読む)

2−トランジスタメモリセル及びその製造方法

本発明は、メモリゲートスタック(1)を有する記憶トランジスタ(1)及び選択トランジスタを有する2-トランジスタメモリセルを基板(50)上に製造する方法であって、トンネル誘電層(51)が前記基板(50)と前記メモリゲートスタック(1)との間にもたらされる方法を提供する。前記方法は、第一の導電層(52)及び第二の導電層(54)をもたらし、前記第二の導電層(54)をエッチし、それによってコントロールゲートを形成し、前記第一の導電層(52)をエッチし、それによってフローティングゲートを形成することによって前記メモリゲートスタック(1)を形成するステップを有する。前記方法は更に、前記第一の導電層(52)がエッチされる前に、前記トンネル誘電層(51)の下に形成されるべきチャネルの方向で前記コントロールゲートに対してスペーサ(81)を形成するステップと、その後、前記第一の導電層(52)をエッチするために前記スペーサ(81)をハードマスクとして使用し、それによって前記フローティングゲートを形成し、それによってフローティングゲートをコントロールゲートに自己整合させるステップとを有することを特徴とする。本発明は、前記コントロールゲート(54)は前記フローティングゲート(52)よりも小さくなり、スペーサ(81)が、前記コントロールゲート(54)に隣接してもたらされるメモリセルも提供する。  (もっと読む)

(もっと読む)

ビットライン間の結合補償のある不揮発性メモリおよび方法

メモリ蓄積ユニットの1つの連続するページをプログラムするとき、メモリ蓄積ユニットは、その目標の状態に達してプログラミングが禁止されるか、或いはそれ以上のプログラミングからロックアウトされる度に、なおプログラムされつつある隣接するメモリ蓄積ユニットに動揺を生じさせる。本発明は、プログラミングの一部として、動揺に対するオフセットがなおプログラムされつつある隣接するメモリ蓄積ユニットに加えられるようになっている回路および方法を提供する。このオフセットは、プログラミングが禁止されているメモリ蓄積ユニットとなおプログラムされつつあるメモリ蓄積ユニットとの隣接するビットライン間の制御された結合によって加えられる。このようにして、高密度メモリ蓄積ユニットを並列にプログラムする動作に固有のエラーが除去されるか、或いは最小にされる。  (もっと読む)

(もっと読む)

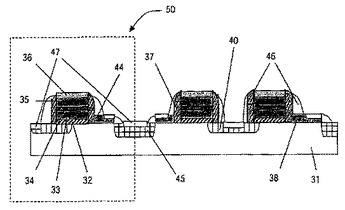

不揮発性メモリ装置を製造する方法及びそれによって得られるメモリ装置

本発明は、ダブル・ゲート・スタック及びシングル・アクセス・ゲートを備える不揮発性メモリ・セル(50)を加工する方法に関する。この方法は、アクセス・ゲートを加工する方法を、自己整合的な、ソース注入とは別のドレイン注入と組み合わせる。本発明の方法は、マスク位置合せ精度を考慮せずに、メモリ装置を消去するための延長されたドレインを自己整合的に注入することを可能にする。さらに、この方法は、さらなるマスクを使用せずにドレイン及びソース注入を互いに異なるドーピングで実施する方法を提供する。  (もっと読む)

(もっと読む)

電荷損失が減少された窒化物層を備えるメモリセル構造及びその製造方法

本発明の一実施形態に従って、半導体基板(210)、半導体基板上に配置された第1シリコン酸化物層(215)、第1シリコン酸化物層上に配置された電荷格納層(220)、電荷格納層上に配置された第2シリコン酸化物層(225)、及び第2シリコン酸化物層上に配置されたゲート層(230)がメモリセル構造に含まれる。例示的な実施形態では、例えば、水素含有量が約0at%〜約0.5at%の範囲に減少されたシリコン窒化物が電荷格納層(220)に含まれる。電荷格納層(220)における水素含有量が減少されることで、結果として電荷損失が減少される。電荷損失が減少された電荷格納層(220)が、メモリデバイスにおける閾電圧シフト、プログラミングデータ損失及びプログラミング性能損失を減少する利点を有し、その結果メモリデバイスパフォーマンスを改善する。  (もっと読む)

(もっと読む)

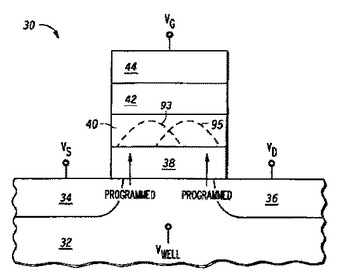

個別電荷蓄積素子を有するメモリのプログラミング

不揮発性メモリ(100)は、個別電荷蓄積素子(40)を有するトランジスタ群(30)から成るアレイを含む。トランジスタに対しては、2ステップ書き込み方法(60)を使用して書き込みを行ない、この方法では、第1ステップ(68)が低ゲート電圧によるホットキャリア注入(hot carrier injection:HCI)書き込みである。第2ステップ(78)を幾つかのメモリセルに対して選択的に利用して注入電荷分布を変え、トランジスタメモリセル内部の各メモリビットの間の電荷分布間隔を大きくする。書き込みを行なう第2ステップは、書き込み操作に長い余分な時間が加わることなく行われる。一の例では、第1ステップにおいて電子を注入し、そして第2ステップにおいてホールを注入する。2つのステップを実行して分布が形成される結果、蓄積媒体の中心部分の電子電荷が取り除かれる。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置、その製造方法、電子カード及び電子装置

【課題】 カップリング比のばらつきを小さくできるNAND型EEPROMを提供する。

【解決手段】 メモリセルの電荷蓄積層17の上層導電部23は、互いに間を設けて形成された一対の立上り部27により構成される内側面29及び外側面31を有する。内側面29側には底面高さ調節層43があり、外側面31側には素子分離絶縁層5がある。このため、半導体基板9の位置(A)のメモリセルと位置(B)のメモリセルとで、立上り部27の高さが異なっていても、電荷蓄積層17と制御ゲートCGとが対向する領域の面積を同じにできる。

(もっと読む)

不揮発性メモリを電荷トラッピングするための改善された消去および読み取り手法

本発明は、不揮発性電荷トラッピング型メモリデバイスのアレイを動作させるための方法を述べる。方法は、アレイの実質的に全ての不揮発性メモリデバイスのブロック消去ステップの前に、アレイの実質的に全ての不揮発性メモリデバイスにブロック書き込みするステップを備える。本発明の利点は、これを行なうことにより、さらなる電荷トラッピング型不揮発性メモリデバイスを、基準セルとして使用できることであり、基準セルは、アレイ内のメモリセルのブロック書き込みおよびブロック消去によって書き込みおよび消去され、したがって、基準セルは、アレイ内のメモリセルと同一の繰り返し履歴を示す。この特性を用いて、読み取りパラメータを目盛りセルの経年変化に適応させることができる。また、対応するデバイスも、提供される。  (もっと読む)

(もっと読む)

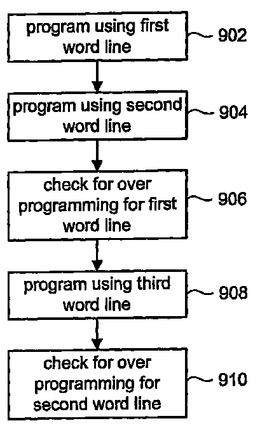

隣接するメモリセルのプログラミングの後にオーバー・プログラミングされたメモリセルを検出する技術

非揮発性半導体メモリシステム(又は他のタイプのメモリシステム)において、メモリセルは、その閾電圧を変更することによってプログラミングされる。システム内の様々なメモリセルに対するプログラミングのタイミングが異なることが原因で、いくつかのメモリセルは、オーバー・プログラミングされてしまう可能性がある。即ち、例えば、セルの閾電圧が、目的とされた値、又は、目的とされた範囲から外れてしまう可能性がある。本発明は、セルに対するプログラミングが原因で、それに隣接する行のメモリセルがオーバー・プログラミングされたか否かを判断することを含んでいる。

(もっと読む)

(もっと読む)

4,321 - 4,330 / 4,374

[ Back to top ]