国際特許分類[H01L43/08]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 電流磁気効果またはこれに類似な磁気効果を利用した装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (4,179) | 磁界制御抵抗 (2,720)

国際特許分類[H01L43/08]に分類される特許

51 - 60 / 2,720

磁気メモリ素子及び磁気メモリ装置

【課題】電流で書き込み動作を行うことができる大容量の磁気メモリ及び磁気メモリ装置を提供する。

【解決手段】磁化が固定された第1の磁性層10と、磁化が可変の第2の磁性層30と、第1の磁性層10と第2の磁性層30との間に設けられた第1の中間層20と、第1の磁性層10と第2の磁性層30とを結ぶ第1の方向に直交する第2の方向に延在し、第2の磁性層30に隣接し、スピン波を伝搬する第1の磁性細線40と、第1の磁性細線40の一端に設けられた第1のスピン波入力部と、第1の磁性細線40の他端に設けられた第1のスピン波検出部と、を備える。

(もっと読む)

スピントランジスタおよびメモリ

【課題】IDP/IDAP比を高めることのできるスピントランジスタおよびメモリを提供する。

【解決手段】本実施形態によるスピントランジスタは、基板上に形成されたソース/ドレインの一方となる第1磁性層と、前記第1磁性層上に設けられチャネルとなる絶縁膜と、前記絶縁膜上に設けられ前記ソース/ドレインの他方となる第2磁性層と、前記絶縁膜の側面に設けられたゲート電極と、前記ゲート電極と前記絶縁膜の前記側面との間に設けられたゲート絶縁膜と、備えている。

(もっと読む)

磁気センサ装置

【課題】 TMR素子の設置環境が高温環境下であってもTMR素子の絶縁破壊を防ぎ、さらにはノイズの影響を受け難く、高いS/N比を得ることができる磁気センサ装置を提供すること。

【解決手段】 トンネル磁気抵抗素子2と、該トンネル磁気抵抗素子2の両端子に一端が接続された一対のリード線3と、一対のリード線3の他端に接続されトンネル磁気抵抗素子2を電圧駆動または電流駆動して抵抗変化を検出する駆動検出回路4とを備え、該駆動検出回路4が、一対のリード線3の他端に接続された一対の出力端子4a間に少なくとも一対のダイオード6aを互いに逆向きにして並列または直列に接続して構成された保護回路6を有している。

(もっと読む)

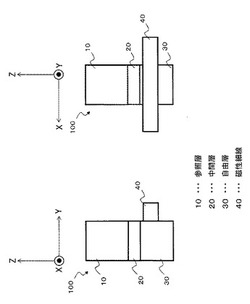

磁気メモリ素子

【課題】実施形態による、磁壁制御が容易な磁気メモリ素子を提供する。

【解決手段】磁気メモリ素子100は、第1方向に延在し、磁壁により隔てられた複数の磁区を有する磁性細線20と、前記磁性細線20に対して前記第1の方向又は前記第1の方向と逆方向に通電可能な一対の第1の電極30と、前記第1の方向に直交する第2の方向において、前記磁性細線20上に設けられた第1の絶縁層40と、前記第2の方向であって前記第1の絶縁層40上に離間して設けられた複数の第2の電極50と、複数の前記第2の電極50と電気的に接続された第3の電極60と、を備える。

(もっと読む)

磁気メモリ素子、磁気メモリ装置、スピントランジスタ、及び集積回路

【課題】 本発明の実施形態によれば、単方向電流で書き込みが可能であり、微細化が可能な磁気メモリ素子、磁気メモリ装置、スピントランジスタ、及び集積回路を提供することができる。

【解決手段】 磁気メモリ素子は、磁化が可変の第1の強磁性層と、第1のバンド及び第2のバンドを有する第2の強磁性層と、前記第1の強磁性層と前記第2の強磁性層との間に設けられた非磁性層と、を備える。

(もっと読む)

磁気抵抗効果素子、ダイオードおよびトランジスタを用いた磁気ランダムアクセスメモリ

【課題】高速動作を可能にする磁気メモリを提供する。

【解決手段】本実施形態の磁気メモリは、スピン注入書込みによって磁化の方向が不変の第1磁性層と、磁化の方向が可変の第2磁性層と、前記第1磁性層と前記第2磁性層との間に設けられたトンネル障壁層とを有する磁気抵抗効果素子と、前記磁気抵抗効果素子の前記第1および第2磁性層の一方の磁性層に電気的に接続された第1配線と、ソース/ドレインの一方が前記磁気抵抗素子の前記第1および第2磁性層の他方に電気的に接続された選択トランジスタと、前記選択トランジスタのソース/ドレインの他方に電気的に接続された第2配線と、前記磁気抵抗素子の前記第1および第2磁性層の他方に電気的に一端子が電気的に接続されたダイオードと、前記ダイオードの他の端子に電気的に接続された第3配線と、前記第3配線に電気的に接続されたセンスアンプと、を備えている。

(もっと読む)

磁気メモリ

【課題】磁気記録層の強磁性体膜が強い垂直磁気異方性を有する磁気メモリを提供する。

【解決手段】磁気メモリは、強磁性体の下地層51と、下地層51上にの第1非磁性52と、第1非磁性52上の垂直磁気異方性を有する強磁性体のデータ記憶層53と、第2非磁性層20を介してデータ記憶層53に接続された参照層30と、下地層51の下側に接した第1、第2磁化固定層41a、41bとを具備する。データ記憶層53は、反転可能な磁化を有し参照層30とオーバーラップする磁化自由領域13と、磁化自由領域13の端に接続され、第1磁化固定層41aに+z方向に磁化固定された第1磁化固定領域11aと、磁化自由領域13の他の端に接続され、第2磁化固定層41bに−z方向に磁化固定された第2磁化固定領域11bとを備える。磁化自由領域13下の第1非磁性52は、第1、第2磁化固定領域11a、11b下の第1非磁性52よりも厚い。

(もっと読む)

磁気抵抗効果素子およびその製造方法

【課題】磁気特性の低下の抑制を図る。

【解決手段】磁気抵抗効果素子は、磁化方向が膜面に対して垂直でかつ不変である第1磁性層33と、前記第1磁性層上に形成されたトンネルバリア層34と、前記トンネルバリア層上に形成され、磁化方向が膜面に対して垂直でかつ可変である第2磁性層35と、を具備する。前記第1磁性層は、上部側に形成され、前記トンネルバリア層の下部に接する界面層32と、下部側に形成され、垂直磁気異方性の起源となる本体層31と、を有する。前記界面層は、内側に設けられた磁化を有する第1領域38と、その外側に前記第1領域を取り囲むように設けられた前記第1領域よりも磁化の小さい第2領域39と、を含む。

(もっと読む)

磁気抵抗効果素子

【課題】磁気メモリの動作不良を抑制する。

【解決手段】本実施形態の磁気抵抗効果素子は、垂直磁気異方性を有し、磁化の向きが可変な記憶層と、垂直磁気異方性を有し、磁化の向きが不変な参照層と、記憶層と参照層との間の非磁性層11と、磁化の向きが不変なシフト調整層と、を含む。参照層は第1の磁化温度依存性LM1を有し、シフト調整層は参照層と異なる第2の磁化温度依存性LM2を有する。メモリ動作温度下において、参照層の漏れ磁場とシフト調整層の漏れ磁場とは互いにキャンセルされ、実装温度下において、参照層の漏れ磁場及びシフト調整層のうち一方に起因するシフト磁界が、記憶層の磁化に印加される。

(もっと読む)

不揮発性抵抗変化素子を含む半導体集積回路とその動作方法

【課題】出力値を変化させる不揮発性抵抗変化素子の状態を、出力動作を止めることなく変化させることができる集積回路を提供する。

【解決手段】不揮発性抵抗変化素子(10)の抵抗を変化させるための書き込み端子(11)と、該抵抗を読み出すための読み出し端子(12)とを別々に有し、電気的にカップリングしていない該書き込み端子と読み出し端子とを用いて書き込み動作と読み出し動作を同時にできる不揮発性抵抗変化素子を有する回路を含む集積回路(50)である。該回路には該不揮発性抵抗変化素子の抵抗値に応じた出力値を出力する出力端子(22)と、該抵抗値を変化させる入力端子(11)を少なくとも有する。該出力端子からの出力の一部を、該入力端子に帰還させることができる。

(もっと読む)

51 - 60 / 2,720

[ Back to top ]