国際特許分類[H01L49/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 27/00〜47/00および51/00に分類されず,他のサブクラスにも分類されない固体装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (1,071)

国際特許分類[H01L49/00]の下位に属する分類

薄膜または厚膜装置 (120)

国際特許分類[H01L49/00]に分類される特許

131 - 140 / 951

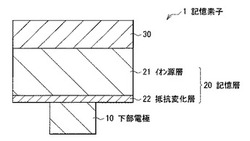

記憶素子および記憶装置

【課題】低電圧および低電流動作時における繰り返し特性が向上した記憶素子および記憶装置を提供する。

【解決手段】下部電極10、記憶層20および上部電極30をこの順に積層した記憶素子1において、記憶層20は、2.8mΩcm以上1Ωcm未満の抵抗率を有するイオン源層21と、抵抗変化層22とを有する。これにより、低電圧または低電流パルスを印加した際の記録状態から消去状態への抵抗変化層の抵抗値の回復が改善され、繰り返し特性が向上する。

(もっと読む)

不揮発性記憶素子および不揮発性記憶装置

【課題】電極と抵抗変化層の界面に小さな突起を形成することなく、低電圧での初期化が可能な不揮発性記憶素子を提供する。

【解決手段】下部電極105と上部電極107との間に介在され、両電極間に与えられる電気的信号に基づいて可逆的に抵抗値が変化する抵抗変化層116を備える。抵抗変化層116は、第1の抵抗変化層1161と第2の抵抗変化層1162との少なくとも2層から構成され、第1の抵抗変化層1161は第1の遷移金属酸化物116bから構成され、第2の抵抗変化層1162は、第2の遷移金属酸化物116aと第3の遷移金属酸化物116cとから構成され、第2の遷移金属酸化物116aの酸素不足度は第1の遷移金属酸化物116bの酸素不足度及び第3の遷移金属酸化物116cの酸素不足度のいずれよりも高く、第2の遷移金属酸化物116a及び第3の遷移金属酸化物116cは、第1の抵抗変化層1161と接している。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】信頼性が高い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、アモルファスカーボンを含むカーボンナノマテリアルが隙間を介して集合したナノマテリアル集合層24と、前記ナノマテリアル集合層24の上面に設けられた上部電極層25と、前記ナノマテリアル集合層24の前記上面に対向する下面に直接的又は間接的に設けられた下部電極層23とを備え、前記ナノマテリアル集合層24が含むアモルファスカーボンの量は、前記下面よりも前記上面の方が少ない。

(もっと読む)

不揮発性半導体記憶装置及びフォーミング方法

【課題】フォーミング処理の時間を低減できる不揮発性半導体記憶装置を提供する。

【解決手段】複数の不揮発性メモリセルは、可変抵抗素子及び整流素子が直列接続されている。制御部は、第1のタイミングにおいて、Nを1以上の整数とするとき複数のワードラインからN本おきに第1のラインを多重選択して選択電位に設定するとともに、少なくとも多重選択されたワードラインに隣接する非選択のワードラインの電位を固定する。制御部は、第2のタイミングにおいて、上記の多重選択されたワードラインを浮遊状態にする。第2のタイミングは、第1のタイミングより後のタイミングである。制御部は、第3のタイミングにおいて、複数のビットラインから1本の第2のラインを選択してフォーミング電位に設定する。第3のタイミングは、第2のタイミングより後のタイミングである。

(もっと読む)

抵抗変化型不揮発性記憶装置

【課題】メモリセルのトランジスタのサイズを最適化可能とした抵抗変化型不揮発性記憶装置を提供する。

【解決手段】下部電極309aと上部電極309cと抵抗変化層309bとからなる抵抗変化素子309と、トランジスタ317とを直列に接続してなるメモリセル300において、トランジスタ317は、ゲート303bと、下部電極309aに電気的に接続されたドレイン又はソース302bと、ソース線SL0に電気的に接続されたソース又はドレイン302aとを有し、ソース線SL0は、互いに平行に配置されかつ1つ以上のビアで接続された複数のレイヤーで形成される配線層305、307からなり、抵抗変化素子309はいずれの配線層305、307よりも半導体基板301からより遠い側に配置され、ビット線BL0は、抵抗変化素子309に対し、半導体基板301からより遠い側に配置され上部電極309cと接続される。

(もっと読む)

不揮発性記憶装置

【課題】良好なスイッチ動作特性を実現する。

【解決手段】不揮発性記憶装置は、平行に配置された複数本のワード線、これらワード線と交差する平行に配置された複数本のビット線、及びワード線とビット線の各交差部のワード線及びビット線間に接続されたメモリセルを有するメモリセルアレイが、隣接するワード線及びビット線を共有して複数積層されて形成される。メモリセルは、直列接続された電流整流素子及び可変抵抗素子を有し、積層方向に隣接する電流整流素子は、互いに逆向きに電流を流し、可変抵抗素子は、下部電極、上部電極、及び下部電極と上部電極との間に形成された導電性ナノマテリアルを含む抵抗変化層を有する。積層方向に隣接する可変抵抗素子の一方は、陰極となる下部電極と抵抗変化層の間に酸化チタンを有し、積層方向に隣接する可変抵抗素子の他方は、陰極となる上部電極と抵抗変化層の間に酸化チタンを有する。

(もっと読む)

不揮発性抵抗変化素子

【課題】電極との間で金属の出し入れが行われることで可逆的に抵抗が変化される抵抗変化層の絶縁性の劣化を抑制する。

【解決手段】抵抗変化層2は半導体元素を有し、第2電極4の金属元素が出し入れされることで可逆的に抵抗変化が可能で、誘電体層3は、第2電極4と抵抗変化層2との間に挿入され、抵抗変化層2よりも第2電極4の金属元素の拡散係数が小さい。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセルアレイに用いられる配線の抵抗を低減することができる半導体記憶装置の製造方法を提供する。

【解決手段】一の実施の形態に係る半導体記憶装置の製造方法は、第1配線層を積層する工程と、第1配線層の上方にメモリセル層を積層する工程と、メモリセル層の上方に、後の研磨工程を減速させるためのストッパ膜を積層する工程とを備える。また、製造方法は、ストッパ膜、メモリセル層、及び第1配線層をエッチングする工程と、ストッパ膜、メモリセル層、及び第1配線層を層間絶縁膜により埋め込んだ後、ストッパ膜に達するまで研磨する工程と、ストッパ膜及び層間絶縁膜に窒化処理を実行して、ストッパ膜及び層間絶縁膜の表面にそれぞれ調整膜及びブロック膜を形成する工程とを備える。そして、製造方法は、調整膜の上方に、エッチングされた第1配線層と交差して各交差部にメモリセルが配置されるように、第2配線層を形成する工程を備える。

(もっと読む)

不揮発性抵抗変化素子

【課題】不揮発性抵抗変化素子の多値化を実現する。

【解決手段】金属元素を有する第1電極11と、半導体元素を有する第2電極13と、金属元素を有する第3電極15と、第1電極11と第2電極13との間に配置され、第1電極11の金属元素が出入りすることで可逆的に抵抗変化が可能な第1抵抗変化層12と、第2電極13と第3電極15との間に配置され、第3電極15の金属元素が出入りすることで可逆的に抵抗変化が可能な第2抵抗変化層14とを設ける。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】 セル面積の縮小が可能であり、かつ、最小加工寸法がメモリセルを構成する材料の膜厚に制限されない半導体記憶装置を提供すること。

【解決手段】 半導体記憶装置において、Y方向に延伸する複数のワード線WL1nの上方に、ゲート絶縁膜104、X方向に延伸するチャネル106、X方向に延伸する抵抗変化素子108を順に形成し、複数のワード線のそれぞれの上方に、チャネルの一部および抵抗変化素子の一部を配置する(MC11n)。係る構成により、セル面積を縮小し、かつ、設計の自由度を担保しうる。

(もっと読む)

131 - 140 / 951

[ Back to top ]