国際特許分類[H01L49/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 27/00〜47/00および51/00に分類されず,他のサブクラスにも分類されない固体装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (1,071)

国際特許分類[H01L49/00]の下位に属する分類

薄膜または厚膜装置 (120)

国際特許分類[H01L49/00]に分類される特許

91 - 100 / 951

不揮発性抵抗変化素子

【課題】抵抗を可逆的に変化させことを可能としつつ、データ保持特性を向上させる不揮発性抵抗変化素子を提供する。

【解決手段】第1電極1と、第2電極3と、可変抵抗層2とを備え、第2電極3は、Al元素が添加された1B族元素を有し、可変抵抗層2は、第1電極1と第2電極3との間に配置され、シリコン元素を有する。可変抵抗層2は非晶質シリコン層であってもよいし、多結晶シリコン層であってもよいし、単結晶シリコン層であってもよい。第1電極1は不純物ドープシリコンおよびTi、Ni、Co、Fe、Cr、Cu、W、Hf、Ta、Pt、Ru、ZrまたはIrや、その窒化物あるいは炭化物あるいはカルコゲナイド材料などを用いることができる。

(もっと読む)

抵抗変化素子の制御方法、および、半導体装置

【課題】抵抗変化素子の閾値電圧のばらつきを生じさせることなく、閾値電圧を低電圧化すること。

【解決手段】印加されたパルス電圧の極性に応じて抵抗値の異なる第1の状態と第2の状態との間で遷移する抵抗変化層と、抵抗変化層の一端に接続された第1の電極と、他端に接続された第2の電極とを備えた抵抗変化素子の制御方法であって、抵抗変化層を第1の状態から前記第2の状態へ遷移させる第1の極性とは逆の第2の極性を有する第1のパルス電圧を、抵抗変化層を第1の状態に保ちつつ、両電極間に印加した後、第1の極性を有する第2のパルス電圧を両電極間に印加して、抵抗変化層を第1の状態から第2の状態へ遷移させる。

(もっと読む)

半導体不揮発性記憶装置およびその製造方法

【課題】高い信頼性で書き込み・消去・読み出しが可能な低コストの半導体不揮発性記憶装置およびその製造方法を提供する。

【解決手段】実施形態の半導体不揮発性記憶装置は、基体Sと、第1の電極2と、機能膜10と、第2の電極50と、を持つ。前記第1の電極2は、前記基体S上に設けられる。前記機能膜10は、前記第1の電極2上に成膜されて記憶媒体をなす。前記第2の電極50は、上面に凸の曲面を有するように、前記機能膜10上または前記機能膜10内に設けられる。

(もっと読む)

混合原子価導電性酸化物を用いたメモリ

【課題】混合原子価導電性酸化物を用いたメモリを提供する。

【解決手段】酸化されていない状態で導電性を有し、酸素欠乏状態で導電性が下がる混合原子価導電性酸化物酸素リザーバ635と、酸素に対する電解質であり、酸素イオンの移動を引き起こすのに有効な電場を促進する電解質トンネル障壁505と、を備える。

(もっと読む)

非揮発性メモリ装置及びセンシング方法

【課題】抵抗変化を利用したマルチレベルのデータをセンシングする非揮発性メモリ装置において、読出し動作の回数を減らし、読出し動作の制御に係わる回路の面積を縮小する。

【解決手段】非揮発性メモリ装置は、1つ以上の単位セルを含んでデータの読出し又は書込みが行なわれるセルアレイと、単位セルに格納されたデータに対応するセンシング電圧SAIと基準電圧REFを比較及び増幅して出力し、ビットラインがプリチャージされた以後にセンシングイネーブル信号SENの活性化区間で、単位セルの抵抗値に応じてセンシング電圧がディスチャージされる時間の差を測定し、データをセンシングするセンシング部100とを含む。

(もっと読む)

メモリ素子スイッチング層形成用組成物、メモリ素子及びメモリ素子スイッチング層形成用重合体

【課題】良好なスイッチング特性を発現するとともに、塗布性に優れたメモリ素子スイッチング層形成用組成物を提供する。

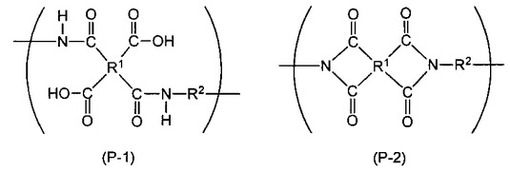

【解決手段】メモリ素子の陽極層と陰極層との間に配置されたスイッチング層を形成するのに用いるメモリ素子スイッチング層形成用組成物において、下記式(P−1)で表される繰り返し単位及び下記式(P−2)で表される繰り返し単位の少なくともいずれかの繰り返し単位(p1)を有する重合体を含むものとする。

(式(P−1)及び式(P−2)中、R1は脂環式構造を有する4価の基であり、R2はトリフェニルアミン構造を有する2価の基である。)

(もっと読む)

抵抗変化型不揮発性メモリセルおよび抵抗変化型不揮発性記憶装置

【課題】電流制御素子が破壊されにくい、抵抗変化型不揮発性メモリセルおよび抵抗変化型不揮発性記憶装置を提供する。

【解決手段】極性の異なる電気的信号を印加することにより抵抗値の異なる複数の抵抗状態の間を可逆的に遷移する抵抗変化素子103と、抵抗変化素子103に直列に接続し、所定の印加電圧の範囲において印加電圧の絶対値が大きくなるにしたがい電圧電流曲線の傾きが大きくなる非線形の電圧電流特性を有する電流制御素子104と、層間絶縁層108、109、110を貫通するホールの内部に形成され、抵抗変化素子103もしくは電流制御素子104の少なくとも一方に接触し、かつ、負荷抵抗部131A、131B、131Cを有する、プラグ105,106,107と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】従来のReRAMを有する半導体装置では、メモリ素子特性にばらつきが生ずるおそれがあった。

【解決手段】基板11を覆う第1の絶縁膜23を形成する工程と、第1の絶縁膜23を貫通する導電プラグ24を形成する工程と、導電プラグ24の上部を一部除去して、導電プラグ24の上面を底面として有し、かつ、一部除去した導電プラグ24に覆われていた部分の第1の絶縁膜23を側壁として有する孔部を形成する工程と、孔部の側壁を覆い、孔部の底面の一部を露出させる側壁絶縁膜25を形成する工程と、孔部の側壁絶縁膜25および底面を覆う可変抵抗膜26を形成する工程と、可変抵抗膜26を覆う導電膜27を形成する工程と、を有する。

(もっと読む)

不揮発性半導体記憶装置および同装置の製造方法

【課題】高抵抗状態と低抵抗状態の抵抗値の比を大きくする素子の構成及び方法並びに素子間ばらつきの低減方法を提供する。

【解決手段】ペロブスカイト酸化物の一面に特定金属が設けられるとともに、前記ペロブスカイト酸化物から前記金属へ当該ペロブスカイト酸化物の酸素が移動することで当該金属の酸化と当該ペロブスカイト酸化物の還元が進行するために必要な活性化エネルギー以上のエネルギーが与えられるように加熱することによって得られる酸素欠乏層領域が前記ペロブスカイト酸化物の前記金属と接触した近傍の領域に存在するようになし、前記金属よりなる一方の電極と前記酸素欠乏層を介して対となる他方の電極間の電圧−電流特性のヒステリシス特性を利用することを特徴とする不揮発性半導体記憶装置である。

(もっと読む)

抵抗記憶装置およびその製造方法

【課題】 電圧印加によりイオンを移動させることで伝導領域を形成・消滅させ、読み出し端子間の抵抗を変化させる抵抗記憶装置において、特性ばらつきが改善された抵抗記憶装置およびその製造方法を提供する。

【解決手段】 本発明の抵抗記憶装置は、イオン源部材と、イオン源部材上に形成された粒状または島状の絶縁体部材と、絶縁体部材上に形成されたイオン伝導体部材と、イオン伝導体部材上に形成された電極部材とを有することを特徴とする。また、本発明の抵抗記憶装置の製造方法は、イオン源部材上に粒状または島状に絶縁部材を形成する工程と、この絶縁部材上にイオン伝導体部材を形成する工程と、イオン伝導体部材上に電極部材を形成する工程とを有することを特徴とする。

(もっと読む)

91 - 100 / 951

[ Back to top ]