国際特許分類[H01L49/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 27/00〜47/00および51/00に分類されず,他のサブクラスにも分類されない固体装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (1,071)

国際特許分類[H01L49/00]の下位に属する分類

薄膜または厚膜装置 (120)

国際特許分類[H01L49/00]に分類される特許

111 - 120 / 951

半導体装置及びその製造方法

【課題】微細なパターンを含む半導体装置の信頼性を向上する。

【解決手段】本実施形態の半導体装置は、素子形成領域100内の半導体素子と、素子形成領域100内から引き出し領域150内に延在する複数の配線WLと、引き出し領域150内の配線WLに接続されるコンタクト部39と、を具備し、配線WLは、n番(nは1以上の整数)の側壁膜のパターンに対応する(n+1)番目の側壁膜のパターンに基づいて形成され、配線WLの配線幅WW又は素子形成領域150内の配線間隔WDに対応する第1の寸法は、リソグラフィの解像度の限界寸法より小さく、露光波長がλ、レンズの開口数がNA、プロセスパラメータがk1で示される場合、第1の寸法は、(k1/2n)×(λ/NA)以下であり、引き出し領域内で互いに隣接する配線WLの間隔WC2に対応する第2の寸法は第1の寸法より大きい。

(もっと読む)

有機分子メモリおよびその製造方法

【課題】メモリセルに流れる電流を制御し、安定した動作と高い信頼性を備える有機分子メモリを提供する。

【解決手段】第1の電極と、第1の電極と異なる材料で形成される第2の電極と、第1の電極と第2の電極との間に設けられる有機分子層であって、有機分子層を構成する抵抗変化型分子鎖の一端が第1の電極と化学結合し、抵抗変化型分子鎖の他端と第2の電極との間に空隙が存在する有機分子層と、を備える有機分子メモリ。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】 メモリセルの微細化を図りつつ、セル電流を確保する。

【解決手段】 実施形態による半導体記憶装置は、ゲート溝15と第1乃至第3の溝19a、19b、18とを有し、第1乃至第3の溝はゲート溝の底面に形成され、第3の溝は第1及び第2の溝の間に形成された半導体基板11と、第1の溝内形成された第1のゲート部21aと第2の溝内形成された第2のゲート部21bと第3の溝内形成された第3のゲート部21cとゲート溝内に形成された第4のゲート部21dとを有するゲート電極21と、を具備する。ゲート電極を有するセルトランジスタTrは、第1及び第3のゲート部間の半導体基板内に形成された第1のチャネル領域Ch1と、第2及び第3のゲート部間の半導体基板内に形成された第2のチャネル領域Ch2と、を有する。

(もっと読む)

抵抗変化型不揮発性半導体記憶装置

【課題】相変化材料配線、抵抗変化材料配線の書き込み電流(Set、Reset電流)、読み出し電流を大幅に低減し、より微細化を可能にし、メモリセルサイズを縮小することを可能にする抵抗変化型不揮発性半導体記憶装置を提供すること。

【解決手段】カルコゲナイド配線GSTと、両端の各々に接続した抵抗配線と、前記抵抗配線のそれぞれの他端を、ソース、ドレインに接続したセルトランジスタとからメモリセルMCを構成し、前記メモリセルを複数直列接続し、一端を、ソースに接続し、ドレインをビット線に接続した選択トランジスタと、前記複数直列接続の他端をソース線に接続し、前記メモリセルのゲートをワード線に接続し、前記選択トランジスタのゲートとブロック選択線に接続したものからセルストリングを構成し、前記セルストリングを複数配設してメモリセルアレイを構成することを特徴とする相変化メモリ。

(もっと読む)

膜形成方法および不揮発性記憶装置

【課題】より良質な膜を形成する。

【解決手段】実施形態の膜形成方法は、下地の上に設けられた酸素及び窒素の少なくともいずれかを含む膜の表面に、酸素及び窒素の少なくともいずれかを含むイオン化されたガスクラスタを照射して、前記ガスクラスタを照射した後の前記膜の密度を前記ガスクラスタを照射する前の前記膜の密度よりも高くする。

(もっと読む)

抵抗変化メモリ

【課題】メモリセルにセレクターを搭載せずに、非選択のメモリセルに流れる回り込み電流を十分に抑制することができる抵抗変化メモリを提供する。

【解決手段】第1電極1a及び第2電極1bと、第1電極1aと第2電極1bとの間に配置された可変抵抗層1cとを有し、少なくとも3つの状態を有するメモリセルMCと、第1電極1aと第2電極1bとの間に電圧を印加して、書き込み、消去、及び読み出しを行う制御回路2とを備える。制御回路2は、書き込み動作時に、第1電極1aと第2電極1bとの間に、第1電圧パルスを与え、前記第1電圧パルスを与えた後、前記第1電圧パルスと極性の異なる第2電圧パルスを与える。

(もっと読む)

不揮発性記憶装置

【課題】記憶容量の増大を図ることができる不揮発性記憶装置を提供する。

【解決手段】実施形態に係る不揮発性記憶装置は、第1の方向に延びる複数本のワード線を含むワード線配線層と、前記第1の方向に対して交差する第2の方向に延びる複数本のビット線を含むビット線配線層と、各前記ワード線と各前記ビット線との間に配置されたピラーと、を備える。前記ピラーは、電流を流すか否かを選択する電流選択膜と、前記電流選択膜に積層された複数枚の抵抗変化膜と、を有する。1枚の前記抵抗変化膜は、金属と、酸素又は窒素と、を含有し、残りの前記抵抗変化膜は、前記金属と、酸素又は窒素と、電気陰性度が前記金属の電気陰性度よりも高い高電気陰性度物質と、を含有する。そして、前記残りの抵抗変化膜における前記高電気陰性度物質の濃度は、前記抵抗変化膜間で相互に異なる。

(もっと読む)

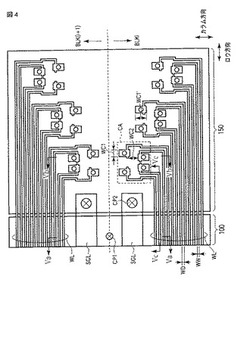

半導体記憶装置

【課題】メモリセルのセルサイズを縮小することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセル(12)と、複数の第1および第2の制御線(112,111)と、複数のワード線(104,105)とを備え、複数のメモリセルは、2つのメモリセルからなるメモリセルペア(10)を備え、各メモリセルペアは、第1および第2の拡散領域(101,102)を有し、ワード線(104)がゲートとなるMOSトランジスタ(15)と、記憶素子(109A,109B)と、第2および第3の拡散領域(102,103)を有し、ワード線(105)がゲートとなるMOSトランジスタ(18)とを備えており、第1の拡散領域(101)から第2の拡散領域(102)へ向かう方向と、第3の拡散領域(103)から第2の拡散領域(102)へ向かう方向とがそれぞれ、第1の制御線(112)に対して傾いている。

(もっと読む)

記憶装置

【課題】アモルファスシリコンを記憶部に用いる記憶装置の動作電圧を低減し、かつ、それを低温プロセスで形成する。

【解決手段】実施形態に係わる記憶装置は、結晶化されたSixGe1−x (0≦x<1)層を含む第1の電極EL1と、金属元素を含む第2の電極EL2と、第1及び第2の電極EL1,EL2間に配置され、アモルファスSi層を含む可変抵抗部VRと、アモルファスSi層内の金属元素を含むフィラメントの長さを制御する制御回路とを備える。

(もっと読む)

記憶素子および記憶装置

【課題】低電圧および低電流動作時における書き込みおよび消去特性が向上した記憶素子および記憶装置を提供する。

【解決手段】下部電極10、記憶層20および上部電極30をこの順に積層した記憶素子1において、記憶層20は、イオン源層21,中間層23および抵抗変化層24が積層されると共に、イオン源層21と中間層23との間または中間層と抵抗変化層との間に、遷移金属あるいはその窒化物を含むバリア層21が設けられている。これにより、イオン源層21からの金属イオンの拡散による酸化膜の生成が抑制され、抵抗値の上昇が抑えられる。

(もっと読む)

111 - 120 / 951

[ Back to top ]