国際特許分類[H01L49/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 27/00〜47/00および51/00に分類されず,他のサブクラスにも分類されない固体装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (1,071)

国際特許分類[H01L49/00]の下位に属する分類

薄膜または厚膜装置 (120)

国際特許分類[H01L49/00]に分類される特許

881 - 890 / 951

金属酸化物素子及びその製造方法

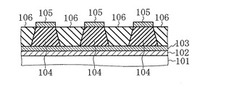

【課題】より安定に状態の保持が得られるなど、金属酸化物から構成された材料を用いて安定した動作が得られる金属酸化物素子を提供する。

【解決手段】単結晶シリコンからなる基板101の上に絶縁層102,共通に設けられた下部電極層103,BiとTiとOとから構成された膜厚30〜200nm程度の複数の金属酸化物層104,金属酸化物層104毎に設けられた上部電極105を備える。また、隣り合う酸化物層104の間が、五酸化タンタルからなる絶縁分離層106により素子分離されている。

(もっと読む)

記憶装置および半導体装置

【課題】不揮発性であって、かつ情報の書き換えが可能であり、また、作製が簡単であり、スイッチング特性に優れ、動作電圧の低い記憶素子、記憶装置および半導体装置を安価で提供することを課題とする。

【解決手段】第一の導電層と、前記第一の導電層に対向する第二の導電層と、前記第一の導電層と第二の導電層間に設置された、少なくとも一種以上の有機化合物を含む層からなる素子において、前記有機化合物は電気化学的にドープ、脱ドープ可能であることを特徴としている。この素子に通電することで、導電層の間に設置された有機化合物を電気化学的にドープする、すなわち電子の授受を行うことでその導電率を3桁から10桁程度上昇させることができる。

(もっと読む)

急激な金属−絶縁体転移素子、その急激な金属−絶縁体転移素子を使用した高電圧ノイズ除去回路、及び、その回路を備えた電気電子システム

基板と、基板の上面及び下面のそれぞれに形成された第1及び第2の急激な金属−絶縁体転移(Metal−Insulator Transition:MIT)構造体と、を備える急激な金属−絶縁体転移素子である。保護されるべき電気電子システムに並列連結され、少なくとも2個の急激な金属−絶縁体転移素子が直列連結された急激な金属−絶縁体転移素子列を備える高電圧ノイズ除去回路である。  (もっと読む)

(もっと読む)

可変抵抗素子を備えた半導体記憶装置

【課題】 第1電極と第2電極の間に可変抵抗体を設けてなり、両電極間に電圧パルスを印加することにより電気抵抗が変化する可変抵抗素子を備えた半導体記憶装置では、製造工程途中で存在する水素若しくは酸素の影響による可変抵抗体の還元反応若しくは酸化反応で、可変抵抗素子の抵抗値が変動してしまうので、抵抗値が揃った可変抵抗素子を備えた半導体記憶装置を再現性良く安定に製造することができなかった。

【解決手段】 可変抵抗体の還元反応を促進する還元種、及び酸化反応を促進する酸化種の透過をブロックする作用を有する材料から構成される反応阻止膜を少なくとも1層有する構造としたので、可変抵抗素子の抵抗値の変動が抑制され、抵抗値のばらつきの少ないかつ制御性の良好な半導体記憶装置を再現性良く実現させることができる。

(もっと読む)

切り換え可能な抵抗器とトランジスタとを備えた不揮発性メモリセル

薄膜トランジスタと、切り換え可能な抵抗器メモリ素子とを直列に備える書き換え可能な不揮発性メモリセルが教示される。切り換え可能な抵抗器メモリ素子は、第1の方向に印加されたセット電圧量を受けると抵抗を減少させ、第1の方向と逆の第2の方向に印加されたリセット電圧量を受けると抵抗を増加させる。好ましい実施形態において、メモリセルは、アレイ、好ましくは、複数のメモリレベルが単一の基板の上に形成されるモノリシックな三次元メモリアレイに形成される。好ましい実施形態において、薄膜トランジスタおよび切り換え可能な抵抗器メモリ素子は、互いに平行なデータ線と参照線との間に電気的に配置される。好ましくは、データ線および参照線に対して垂直に延びる選択線がトランジスタを制御する。  (もっと読む)

(もっと読む)

メモリセル及び半導体記憶装置及びその製造方法

【課題】 低電圧で動作可能であり、且つ、高集積化が可能なメモリセル及び該メモリセルを用い、メモリセルアクセス時において、隣接するメモリセルへのリーク電流が生じず、更に、メモリセルの特性のばらつきを抑制した高性能な半導体記憶装置を提供する。

【解決手段】 第1電極119と第2電極118の間に可変抵抗体113を挟持してなる可変抵抗素子と、可変抵抗素子に流れる電流を制御可能なトランジスタ素子を備え、トランジスタ素子と可変抵抗素子が、可変抵抗素子の第1電極119と可変抵抗体113と第2電極118の積層方向と同方向に積層されてなり、可変抵抗素子の第1電極119と第2電極118の何れか一方と、トランジスタ素子の1つの電極107bが接続している。

(もっと読む)

急激な金属−絶縁体転移を利用したメモリ素子及びその動作方法

構造変化を経ずに均一な薄膜を保持して、高速スイッチング動作が可能なメモリ素子及びその動作方法を提供する。その素子及び方法は、電子のエネルギー変化により急激に金属−絶縁体転移をする金属−絶縁体転移物質層にコンタクトさせられ、熱により融解されて転移物質層に導電性経路を形成する少なくとも2個の電極を備える。  (もっと読む)

(もっと読む)

ReRAM用多層二元酸化膜の形成方法

本発明は、ReRAM素子用多層二元酸化薄膜の形成方法に関する。この方法は、基板上に下部電極膜を形成する段階と、真空の雰囲気で上記下部電極膜上に金属膜を形成する段階と、真空の雰囲気で上記金属膜を二元酸化膜に酸化させる段階と、

上記金属膜の形成段膜と上記酸化する段階を繰り返して所望の厚さの多層薄膜を形成する段階と、上記多層薄膜上に上部電極膜を形成する段階とを含む。本発明によれば、真空状態で金属膜の形成と酸化工程を行うため、工程が簡単で表面汚染の恐れが無く従来のペロブスカイト系より優れた高効率の非揮発性メモリ素子を実現できる。

(もっと読む)

高度に分解されたドメインを書き込むための媒体

本発明によるシステムは、媒体と結合可能なチップを含むことができ、媒体は、基板とオーバーコートとの間に配置された、一実施形態においては相変化材料(或いは、他の実施形態においては極性依存メモリ材料又は他のメモリ材料)を含む。オーバーコートは、導電部分と実質的に非導電部分とを有する共堆積された膜であり、この共堆積膜は、オーバーコートを横切るよりもオーバーコートを貫通する方が電流をより効果的に導通する。オーバーコートは、材料の構造が無秩序になるのに十分な温度までチップの真下の相変化材料の部分を加熱するように、電流を実質的に導く。次に、電流が相変化材料から除去され、相変化材料が急速に冷却され、結晶バルク構造よりも高い抵抗率を有するドメインを形成する。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置

【課題】 可変抵抗素子からなるクロスポイント型のメモリセルアレイに対する書き込みまたは消去動作に伴う非選択メモリセルの抵抗変化を抑制し、読み出しマージンの大きな不揮発性半導体記憶装置を提供する。

【解決手段】 メモリセルアレイ3の中から、選択メモリセルM0を選択するメモリセル選択回路と、選択ワード線と選択ビット線に対し、行書き込み電圧と列書き込み電圧を各別に印加し、非選択ワード線と非選択ビット線に対し、行書き込み阻止電圧と列書き込み阻止電圧を各別に印加することにより、選択メモリセルM0の両端にのみ書き込みに十分な書き込み電圧を印加する書き込み電圧印加回路を備え、書き込み電圧印加回路が、選択メモリセルM0に対する書き込み電圧の印加に伴って、選択メモリセルM0以外の非選択メモリセルM1、M2の両端に印加された電圧と逆極性の書き込み補償電圧を、非選択メモリセルM1、M2の両端に印加する。

(もっと読む)

881 - 890 / 951

[ Back to top ]