国際特許分類[H01L49/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 27/00〜47/00および51/00に分類されず,他のサブクラスにも分類されない固体装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (1,071)

国際特許分類[H01L49/00]の下位に属する分類

薄膜または厚膜装置 (120)

国際特許分類[H01L49/00]に分類される特許

921 - 930 / 951

調整可能なエネルギバンドギャップを有する半導体装置

本発明は、エネルギバンドギャップが可逆的に変化されることができる半導体装置に関する。本発明の発想は、例えば、相変化材料307のような、適切にアドレス指定された場合に体積の可逆的変化を呈する材料307と機械的に接触状態にある半導体材料306に基づく装置を提供することにある。前記装置は、例えば、発光、スイッチ及びメモリの用途において実施されることができる。前記半導体材料は、前記相変化材料に局所的な体積の変化を生じさせることにより、可逆的に歪まされることができる。前記半導体材料の得られるバンドギャップの変化は、例えばLED又はレーザから、発せられる光の色を調整するのに利用されることができる。他の分野の用途においては、半導体接合における接触抵抗が制御されることができ、このフィーチャは、メモリ及びスイッチにおいて非常に有利である。  (もっと読む)

(もっと読む)

プログラム可能な不揮発性抵抗切り替えデバイス

【課題】 複数の抵抗状態の間で可逆的に切り替えることができるメモリ素子を含むデバイスのような超小型電子デバイスを提供する。

【解決手段】 メモリ素子は、第1の数の電極と、2電極のサブグループ間の第2の数の導電性チャネルとを含み、チャネルは、異なる状態間で可逆的に切り替え可能な電気抵抗を呈し、前記第1の数は2より大きく、前記第2の数は前記第1の数を2で割った数より多い。導電性チャネルは、遷移金属酸化物材料において与えられ、それは、電極と遷移金属酸化物材料との間の界面における切り替え現象に起因する可逆的に切り替え可能な抵抗を呈する。

(もっと読む)

電界で分極される材料

本書に記載する発明には、供与体サブユニット(12);受容体サブユニット(16);及び芳香族架橋性サブユニット(20)であって、1つ又は複数の芳香族架橋性サブユニット20を含み且つ受容体サブユニット16を芳香族架橋性サブユニット20に結合するための芳香族架橋性サブユニット(20)、を含んで成る分子スイッチ(10)が包含され、この場合、芳香族架橋性サブユニット20は、低い電界電圧において分子スイッチ10を分極及び脱分極させるように配座する。 (もっと読む)

分子メモリとそのプロセスシステムおよびプロセス方法

分子メモリ、すなわち、電荷蓄積用分子を組み込んだメモリについて開示した。分子メモリセル、分子メモリアレイ、および分子メモリを含む電子デバイスについても開示した。また、分子メモリ製造のためのプロセスシステムおよびプロセス方法についても同様に開示した。さらに、半導体デバイスおよび相互配線を分子メモリとモノリシックに製造することを可能にする分子メモリ製造方法についても開示した。  (もっと読む)

(もっと読む)

混合原子価導電性酸化物を用いたメモリ

【課題】

【解決手段】混合原子価導電性酸化物を用いたメモリが開示されている。そのメモリは、酸素欠乏状態で導電性が下がる混合原子価導電性酸化物と、酸素に対する電解質であり、酸素イオンの移動を引き起こすのに有効な電場を促進する電解質トンネル障壁と、を備える。

(もっと読む)

可変データ保持時間を有するポリマーメモリ

ポリマーメモリセル(102、200)がその内部に記憶されたデータ用の可変保持時間を呈することができるようにするシステムおよび手法が提供される。保持時間のそのような設定は、ポリマーメモリセル(102、200)に採用されたプログラミングモードおよび/または材料のタイプに依存し得る。短い保持時間は、低電流または低電界によってポリマーメモリセル(102、200)をプログラミングすることによって得ることができる。同様に、長い保持時間は、ポリマーメモリセル(102、200)をプログラミングするために高電流または高電界を採用することによって得ることができる。  (もっと読む)

(もっと読む)

ポリマーメモリセルのプログラミングしきい値を調節するためのシステムおよび方法

ポリマーメモリセル(215、640)の動作に関連するしきい値を、作製後の段階中に調整された電界および/または電圧パルス幅をそれに印加することによって調節するためのシステムおよび方法が提供される。プログラミングしきい値のそのようなカスタマイゼーションは通常、回路設計の柔軟性を高めるために、メモリセル(215、640)をプログラミングするどのサイクルででも得ることができる。したがって、この発明は、電流−電圧ドメインおよび/または周波数−時間ドメインの双方を供給して、ポリマーメモリセル(215、640)のプログラムしきい値の調節を容易にする。  (もっと読む)

(もっと読む)

抵抗可変メモリ・ディバイスと製造方法

【構成】抵抗可変メモリ・ディバイスのアグロメレーション防止および温度安定性を実現する方法および装置である。一実施形態によれば,少なくとも1つの錫−カルコゲナイド層と少なくとも1つのカルコゲナイド・ガラス層とが近接した抵抗可変メモリ・ディバイスが提供される。この発明はさらに,そのようなメモリ・ディバイスの形成方法に関する。 (もっと読む)

自己スイッチングメモリデバイス

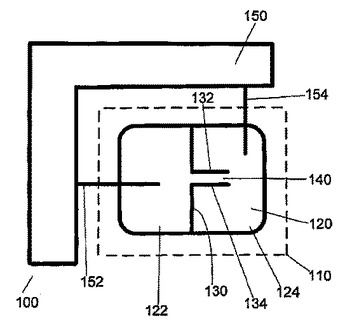

メモリデバイス、及び関連する製造及び動作の方法を説明している。該メモリデバイスは、移動電荷キャリアを支持する基板(120)を具えている少なくとも1つのメモリユニットを含む。該基板表面上には絶縁部(130、132、134)が形成され、該絶縁部の両側に第1及び第2基板領域(122、124)を形成している。該第1及び第2基板領域は、絶縁部によって形成された細長チャネル(140)によって接続されている。メモリユニットは、前記第1及び第2領域間の所定の電位差でチャネルが第1及び第2領域間に第1のコンダクタンスを与える第1の状態と、前記所定の電位差でチャネルが第1及び第2領域間に第2の異なるコンダクタンスを与える第2の状態との間で切り換え可能である。メモリユニットを第1の状態に変更するため、前記メモリユニットの第1及び第2領域に第1の電位差を、そしてメモリユニットを第2の状態に変更するため第2の異なる電位差を印加するよう、書き込み回路(150)が構成されている。メモリユニットの状態を読み出すため、メモリユニットの第1及び第2領域に前記所定の電位差を印加するよう、読み出し回路(150)が構成されている。  (もっと読む)

(もっと読む)

スイッチャブルメモリダイオード−新メモリデバイス

メモリセルと一体化されたダイオード構成要素を形成し、メモリセルのアレイのプログラミングを容易にするシステムおよび方法が提供されている。このようなダイオード構成要素は、非対称の半導体特性を有するパッシブ層とアクティブ層とを備えたメモリセルのpn接合の一部であり得る。そのような配置にすることで、トランジスタタイプの電圧制御の数と関連する電力消費を減らし、一方で、パッシブアレイの一部として個々のメモリセルのプログラミングを可能にする。さらに、システムにより、メモリセルがウェハ表面上に効率的に配置され、かつ、回路設計に利用できるダイスペース量を増加する。  (もっと読む)

(もっと読む)

921 - 930 / 951

[ Back to top ]