国際特許分類[H03B5/02]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 振動の発生,直接のまたは周波数変換による振動の発生,スイッチング動作を行なわない能動素子を用いた回路による振動の発生;このような回路による雑音の発生 (3,506) | 出力から入力への再生帰還による増幅器を用いた振動の発生 (3,166) | 細部 (241)

国際特許分類[H03B5/02]の下位に属する分類

国際特許分類[H03B5/02]に分類される特許

101 - 110 / 122

クロック信号の生成及び分配装置

【課題】 数ギガヘルツ以上の高周波域においても、高精度のクロック信号を生成し分配可能なクロック生成分配装置を提供すること、及び20GHzに達するような高周波域においても、各電圧制御発振器が同一位相で発振し、希望する周波数のクロック信号が生成でき、高周波クロック信号を、より安定にチップ内の各部に分配する分散VCO型クロック生成分配装置を提供すること。

【解決手段】 各電圧制御発振器としてLC共振型電圧制御発振器を採用し、さらにその発振ノード間の接続配線のインダクタ成分を相対的に小さくして、あるいは、LC共振発振器を注入同期により同期して発振させることにより、各LC共振型電圧制御発振器が安定して同一位相で発振するようにする。

(もっと読む)

電圧制御発振回路

【課題】バッファ増幅器の電源系を分離して定電圧発生回路と接続し、一部を共用化して電源電圧を下げずに電源ノイズの影響を抑制し小型化する。

【解決手段】差動バッファ増幅器11は、エミッタが共通接続のバイポーラトランジスタ24,25と電源電圧Vccに接続の負荷抵抗26,27からなり、共通エミッタは差動発振器12のインダクタの中点に接続される。差動発振器12のインダクタ中点には接地容量23が接続され、不要な干渉を抑え、ノイズ回り込みを抑制する。差動発振器12の発振信号は結合容量21,22を介して差動バッファ増幅器11の出力端子13から出力される。バイポーラトランジスタ24,25のベースは、抵抗28,29を介して定電圧発生回路61と接続され、電源系と分離してバイアス電圧が供給される。これにより電源ノイズの影響を抑制し、電源電圧を下げることなく出力ができ、消費電流を抑え、かつ電源ノイズの影響を抑制する。

(もっと読む)

集積回路

【課題】従来の発振器用集積回路では、低振幅の出力波形を要求された場合に、出力増幅回路トランジスタ対のゲート・ソース間電圧が十分に確保できず、大きな負荷を駆動できないという問題があった。

【解決手段】 出力増幅回路112のPチャネルトランジスタ110およびNチャネルトランジスタ111のゲートを、コンデンサ106および107により発振回路104の出力に交流的に結合するとともに、抵抗108および109を介してPチャネルトランジスタ110のゲートはGND電位に、Nチャネルトランジスタ111のゲートは電源電位にバイアスされていることにより、これらのトランジスタのゲート・ソース間電圧が充分に確保され、大きな負荷を駆動できるようにしたことを特徴とする集積回路。

(もっと読む)

高い直線性を有する直交発振器

本発明は、同相信号と直交信号の発振周波数を制御する発振回路及び方法に関するものである。第1差動発振回路及び第1差動結合回路を有する第1発振器手段(2)を設けて直交信号を発生する。さらに、第2差動発振回路及び第2差動結合回路を有する第2発振器手段(4)を設けて同相信号を発生する。周波数制御手段を設けて、第1及び第2発振器手段のコモンモード電流及びテール電流を制御することによって、同相信号及び直交信号の発振周波数を変化させる。これにより、高い直線性を有する高周波IQ発振器が得られる。  (もっと読む)

(もっと読む)

2バンド発振器

【課題】 2つの発振信号を切り替えて共通の端子から出力する場合に、発振信号の減衰を少なくする。

【解決手段】 第1の周波数帯の発振信号を出力する第1の発振トランジスタ11と、第1の発振トランジスタ11のコレクタに電源を供給する第1のインダクタ12と、第1の発振トランジスタ11の動作を切り替える第1のスイッチ素子16と、第2の周波数帯の発振信号を出力する第2の発振トランジスタ21と、第2の発振トランジスタ21のコレクタに電源を供給する第2のインダクタ22と、第2の発振トランジスタ21の動作を切り替える第2のスイッチ素子26と、第1の周波数帯の発振信号又は第2の周波数帯の発振信号を外部に出力する出力端子30とを備え、第1のインダクタ12と出力端子30との間に第1のスイッチ素子16を介挿し、第2のインダクタ22と出力端子と30の間に第2のスイッチ素子22を介挿した

(もっと読む)

発振装置及び発振方法

【課題】 従来の発振装置では、CR発振回路は、水晶発振回路の発振の起動の支援を充分に適切に行うことができなかった。

【解決手段】 本発明に係る発振装置は、水晶発振子により規定される周波数を有する第1の信号を発振する水晶発振回路と、前記水晶発振回路が前記第1の信号を定常的に発振するまでの過渡期において、前記周波数と実質的に同一な第2の周波数を有する第2の信号を生成し、当該第2の信号を前記水晶発振回路に供給するCR発振回路とを含む。

(もっと読む)

発振回路モジュール

【課題】 信号出力部のトランジスタのコレクタ−ベース間のアイソレーションを確保して、出力レベルおよび周波数負荷安定度を高めた発振回路モジュールを構成する。

【解決手段】 第1の電圧制御発振回路VCO1のバッファ用トランジスタQ12のベースに接続したベースバイアス回路(R11,R12,R13)がスイッチSW1を介して接続される外部電源端子VB2と、トランジスタQ12のコレクタが接続される外部電源端子VB1とを異ならせる。

(もっと読む)

電圧制御発振回路、およびその調整方法

【課題】 簡易な回路構成により、構成素子の特性の製造バラツキにかかわらず、出力特性のバラツキを抑制する調整が可能な、電圧制御発振回路、およびその調整方法を提供すること。

【解決手段】 低域通過フィルタ15、高域通過フィルタ16は、電圧制御発振回路11を構成する素子と同一構造の素子で構成され、所定の相関関係が形成される。補正素子14は、電圧制御発振回路11において発振周波数制御信号VTが入力される主素子と並列に接続される。目標ゲイン値TGにおいて、低域通過フィルタ15と高域通過フィルタ16との周波数−ゲイン特性は互いに逆の傾きを有して交差する。容量値が低くばらつく場合、基準周波数fREFにおいて、出力信号SL2がSH2よりも出力レベルが大きくなり、出力レベル差LD2が発生し、LD2に応じた調整信号VCNT2が出力され、発振周波数fVCOが低くされる。

(もっと読む)

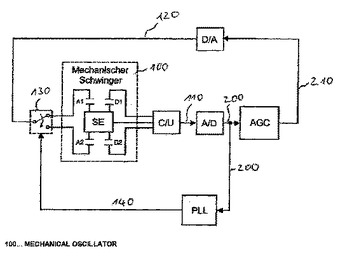

振動回路

本発明はアナログの振動素子(SE)を備えた振動回路に関する。本発明の核となる着想は、振動回路が少なくとも1つのアナログ・ディジタル変換手段(A/D)を有することである。さらに本発明は、機械的な発振器(SE)が固有周波数での振動を行う振動回路の作動方法に関する。振動振幅は測定され(D1,D2)、ディジタル化される(A/D)。ディジタルの振幅制御器(AGC)を用いてディジタル制御信号(210)が形成され、このディジタル制御信号(210)からまた駆動信号(120)が形成され、この駆動信号(120)は駆動部(A1,A2)を用いて機械的な発振器(SE)を駆動させる。この制御回路は振動振幅を安定させる。  (もっと読む)

(もっと読む)

電圧制御発振器及びそれを用いたPLL回路並びに周波数変調器

【課題】 安定なPLLを構成できる電圧制御発振器を得る。

【解決手段】 複数の周波数帯域を出力周波数帯域とすることができる電圧制御発振器1において、その電圧制御発振部3の前段に電圧変換部2を設け、制御部4が、電圧制御発振器1の周波数制御電圧S1−出力周波数S2変換特性を線形とすると共に電圧制御発振器1の出力周波数帯域それぞれにおける上記変換特性の傾きを略同一とすべく、出力周波数帯指定信号S3により指定される周波数帯域に応じて電圧変換部2の電圧変換特性を制御する。

(もっと読む)

101 - 110 / 122

[ Back to top ]