国際特許分類[H03F3/26]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 増幅器 (10,074) | 増幅素子として電子管のみまたは半導体装置のみをもつ増幅器 (6,434) | プッシュプル増幅器;そのための位相分割器 (74)

国際特許分類[H03F3/26]の下位に属する分類

真空管のみをもつもの (2)

国際特許分類[H03F3/26]に分類される特許

11 - 20 / 72

電力増幅器

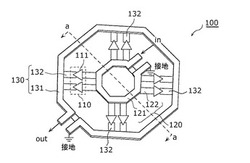

【課題】入力の整合回路での損失の低減、並びに、回路の簡略化及び小型化が可能な電力増幅器を提供する。

【解決手段】電力増幅器100であって、第1金属配線である環状1次コイル121と、複数の第2金属配線である複数の直線2次コイル122とを有し、入力インピーダンスの整合をとるとともに、入力信号を複数の分配信号に分配する入力側トランスフォーマ120と、複数の分配信号の1つを増幅する1対のトランジスタ111をそれぞれが備える複数のプッシュプル増幅器110と、第3金属配線である環状2次コイル131と、複数の第4金属配線である複数の直線1次コイル132とを有し、増幅された複数の分配信号を合成するとともに、出力インピーダンスの整合をとる出力側トランスフォーマ130とを備え、1対のトランジスタ111の2つの入力端子は、第2金属配線を介して互いに接続され、2つの出力端子は、第4金属配線を介して互いに接続される。

(もっと読む)

ゲート接地型増幅回路

【課題】高速低消費電力の電流検出型センスアンプの実現には、低バイアス電流でゲイン帯域積が大きな増幅器をゲート接地型トランジスタに設ける必要がある。

【解決手段】ソースが電流入力端子Iin1,Iin2、ドレインが負荷8,9および電圧出力端子Vout1,Vout2に接続されたゲート接地型トランジスタペアM1,M2のゲート・ソース間に、トランジスタM3とM5およびM4とM6の2組のソースが共通のプシュプル型CMOS反転増幅器で構成される差動増幅器の共通ソースに定電流トランジスタM7が設けられた差動増幅器AMPを設ける。

(もっと読む)

出力バッファ回路およびそれを用いたドライバ回路

【課題】 入出力信号が変化する際の過渡期間に出力バッファを構成するトランジスタへのバイアス電流を一時的に増強することで、バッファ回路全体の定常的なバイアス電流を抑制しつつ、高スルーレートが得られるバッファ回路を提供する。

【解決手段】 ドライバ回路200は信号レベル発生回路100により発生した信号SGOを出力バッファ回路110を駆動する回路150(プリバッファ回路)を介し、出力バッファ回路110により伝送線路120を駆動することで測定対象回路DUT140に伝える。プリバッファ回路150とこれを模擬したレプリカバッファ回路160とを互いに並列に備え、信号SGOが変化する際の入出力新信号の過渡期間において、レプリカバッファ回路160の出力電流に基づいて出力バッファ回路110の出力段トランジスタQN12、QP22の入力バイアス電流を一時的に増強する。

(もっと読む)

増幅器及び無線機器

【課題】増幅器の入出力特性の直線性が悪化することを防ぐこと。

【解決手段】一対のFET素子Q1,Q2の出力側の各々の間に1次側の両端が接続され、2次側の両端よりFET素子Q1,Q2から出力される信号を降圧した降圧信号を出力する帰還用トランスL3と、FET素子Q1,Q2の入力側の各々と、FET素子Q1,Q2の入力側の位相と同相となる降圧信号を出力する帰還用トランスL3の2次側の各々との間に、FET素子Q1,Q2の入力側に向かって整流する方向に接続された整流用ダイオードD1,D2と、整流用ダイオードD1,D2を介してFET素子Q1,Q2の入力側にバイアス電圧またはバイアス電流を供給するバイアス回路と、を備える。

(もっと読む)

クラス特性可変増幅器

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

クラスAB増幅器

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

誘導コモンモード減結合のあるプッシュプル増幅器

増幅すべき入力信号(e)を出力信号(a)に増幅するためのプッシュプル増幅器が一つの第1の及び一つの第2の増幅素子(1、1’)有する。前記2つの増幅素子(1、1’)のそれぞれが一つの電流放出電極(2、2’)、一つの集電電極(3、3’)、及び一つの電流制御電極(4、4’)を有する。前記増幅素子(1、1’)の前記電流制御電極(4、4’)に、それぞれの入力端子(6、6’)を介して、及び、それぞれの前記入力端子(6、6’)とそれぞれの前記電流制御電極(4、4’)との間に配置されたそれぞれの入力インダクタンス(5、5’)を介して、前記入力信号(e)が供給される。前記集電電極(3、3’)は、それぞれの供給インダクタンス(7、7’)を介して一つの共通の供給電圧(V+)に接続される。前記増幅素子(1、1’)の前記電流放出電極(2、2’)は、それぞれのコンデンサ(8、8’)を介してそれぞれもう一方の前記増幅素子(1’、1)の前記集電電極(3’、3)に接続される。前記電流放出電極(2、2’)は、前記出力信号(a)をピックアップ可能である出力端子(9、9’)に接続される。前記電流放出電極(2、2’)は、それぞれの出力インダクタンス(10、10’)を介して基準電位に接続されている。前記増幅素子(1、1’)の前記供給インダクタンス(7、7’)は、それぞれもう一方の前記増幅素子(1’、1)の前記入力インダクタンス(5’、5)及び前記出力インダクタンス(10’、10)に誘導結合される。  (もっと読む)

(もっと読む)

出力回路

【課題】構成素子数を最小限に抑えて消費電流の増加を抑え、且つ過渡応答時のクロスオーバー歪を改善する。

【解決手段】NチャネルMOSトランジスタM1,M2,M6と、PチャネルMOSトランジスタM3,M4,M5を備える出力回路において、ドレインとゲートがMOSトランジスタM2のドレインおよびトランジスタM5のゲートに接続され、ソースがMOSトランジスタM4のドレインに接続されたMOSトランジスタM7を設けた。

(もっと読む)

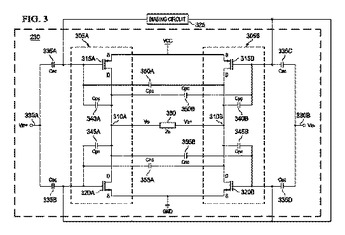

入力抵抗が改善され、コモンモード制御された増幅器

第1出力(Vo−)を規定し、第1入力端子(330A)に結合されるゲートを各トランジスタ(315A、320A)が有する第1対のトランジスタ(305A)、第2出力(Vo+)を規定し、第2入力端子(330B)に結合されるゲートを各トランジスタ(315B、320B)が有する第2対のトランジスタ(305B)、第2出力端子(310B)に及び第1対のトランジスタの第1トランジスタ(315A)のゲートに結合される第1キャパシタ(350A)、第2出力端子(310B)に及び第1対の第2トランジスタ(320A)のゲートに結合される第2キャパシタ(355A)、第1出力端子(310A)に及び第2対の第3トランジスタ(315B)のゲートに結合される第3キャパシタ(350B)、及び第1出力端子(310A)に及び第2対の第4トランジスタ(320B)のゲートに結合される第4キャパシタ(355B)を含む増幅器(230)。

(もっと読む)

(もっと読む)

電流電圧変換合成出力装置

【課題】負帰還回路を用いずにDAコンバーターの電流出力を電圧出力に高精度で変換しプッシュプル合成して高品質の信号出力を得る、構成簡易で安価な電流電圧変換合成出力装置。

【解決手段】夫々エミッタ入力・ベース電圧固定(接地)・コレクタ出力動作の第1、第2のトランジスタQ10、Q11と、第1〜第3のカレントミラー回路CM1〜CM3を組み合わせて用いる。 カレントミラー回路CM1、CM2は夫々トランジスタQ10、Q11の各コレクタ出力をカレントミラー電流出力する。カレントミラー回路CM3はカレントミラー回路CM1の出力をカレントミラー電流出力する。カレントミラー回路CM2、CM3の各出力の共通接続点とGND間に、抵抗とコンデンサの並列回路が接続される。DAコンバーターからの互いに極性が逆の電流出力信号を、各トランジスタQ10、Q11のエミッタに入力し、カレントミラー回路CM2、CM3の各出力の共通接続点に電流電圧変換された電圧出力信号を得る。

(もっと読む)

11 - 20 / 72

[ Back to top ]