国際特許分類[H03F3/26]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 増幅器 (10,074) | 増幅素子として電子管のみまたは半導体装置のみをもつ増幅器 (6,434) | プッシュプル増幅器;そのための位相分割器 (74)

国際特許分類[H03F3/26]の下位に属する分類

真空管のみをもつもの (2)

国際特許分類[H03F3/26]に分類される特許

61 - 70 / 72

増幅器

常に信号の増幅動作を行うキャリア増幅器と、高電力出力時のみに動作するピーク増幅器と、キャリア増幅器とピーク増幅器の出力を合成して出力する合成器と、入力信号をキャリア増幅器側とピーク増幅器側に分配する分配器とを含んで構成される。キャリア増幅器およびピーク増幅器は1個のパッケージ1(1パッケージトランジスタ)に内蔵される。  (もっと読む)

(もっと読む)

負荷駆動回路

【課題】位相特性が良好であり、しかも低価格のLSIチップとして実現可能な負荷駆動回路を提供すること。

【解決手段】終段増幅回路(AMP0)の出力素子(P1,N1)の制御入力端子(GP1,GN1)と当該負荷駆動回路の出力端子(OUT)との間に非直線抵抗素子(P2,N3)とスイッチ素子(N2,P3)との直列回路を挿入する。非直線抵抗素子は、印加電圧値が増加するに連れて抵抗値が減少し、かつ印加電圧値が減少するに連れて抵抗値が増加する非直線特性を有する。スイッチ素子は、その出力素子が終段増幅回路内において、高電位側又は低電位側のいずれに配置されているかに対応して、入力信号の高電位期間又は低電位期間に限り選択的にオン状態となるようにスイッチング制御される。

(もっと読む)

高出力電力増幅モジュール

【課題】配線パターン内の高周波信号の位相差を小さくし、電流分布を線対称にすることで、電力損失を低減すると共に、且つ高出力電力増幅モジュールの設計を容易に行うことが可能な高出力電力増幅モジュールを提供する。

【解決手段】少なくとも一つの電力増幅用半導体素子が内蔵された半導体モジュール1と、半導体モジュールに接続された入力側伝送線路14、15と、半導体モジュールに接続された出力側伝送線路16、17と、入力側伝送線路および出力側伝送線路に各々接続されたインピーダンス整合用の回路素子10、11、32〜35とを備える。インピーダンス整合用の回路素子は、入力側伝送線路および出力側伝送線路を構成する金属配線パターンの少なくとも一方について、信号の進行方向に対する両側端部に各々、少なくとも1個が実装される。

(もっと読む)

プッシュプルバッファ増幅器とソースドライバ

【課題】高速充放電速度で低消費電力を達成するプッシュプルバッファ増幅器とソースドライバを提供する。

【解決手段】バッファ増幅器内で、N型コンパレータとP型コンパレータが入力信号と出力信号を比較する。第1インバータと第2インバータの入力端子がそれぞれN型コンパレータとP型コンパレータの第1出力端子に接続する。第1電圧線が出力負荷に充放電するように、第1トランジスタと第4トランジスタはそれぞれN型コンパレータの第2出力端子と第2インバータの出力端子により制御される。第2電圧線と第2電圧線が出力負荷に充放電するように、第2トランジスタと第3トランジスタはそれぞれP型コンパレータの第2出力端子と第1インバータの出力端子により制御される。

(もっと読む)

増幅器出力ステージを制御する制御回路を備える集積回路装置及びそのドライビング方法

【課題】出力電圧を発生させる増幅回路を備える集積回路装置を提供する。

【解決手段】バイアス制御回路(215,216)は、制御信号(SW)の状態に基づいてその出力からバイアス制御電圧(VB1,VB2)または出力電圧(VOUT+,VOUT−)を選択的に発生させる。出力ステージドライバー回路(213)は、バイアス制御回路の出力から発生した電圧に応答して動作する。

(もっと読む)

変調機能を有する増幅装置

【課題】例えば数GHzから十数GHz程度の高周波を送信する送信装置などに有用な、変調器や増幅器などを集積して構成されるIC回路の小型化や消費電力の低減を図る。

【解決手段】本発明の変調機能を有する増幅装置の回路構成は、アクティブバラン部1とプッシュプル増幅部2とLCバラン部3の3つの部分に分類することができる。アクティブバラン部1は、主に、変調信号入力回路110と図中の差動増幅器などから構成される。アクティブバラン部1は基本的には差動増幅器であると考えることができるが、高周波用途であるのでインダクタやキャパシタを多く含んでおり、高周波のマッチングを考慮して構成されている。差動増幅器には2つの入力端子ta とtb があり、通常は位相が互いに180°異なる2つのキャリヤを入力するバランス入力と、片方の入力端子は接地してもう一方のみにキャリヤを入力するシングル入力の2つの使い方が可能である。

(もっと読む)

電力増幅回路および電力増幅器

【課題】 歪のない安定した出力を得られる安価な電力増幅回路および電力増幅器を提供する。

【解決手段】 NチャンネルFET1のソースとNチャンネルFET2のドレインを共通接続し、この接続点に負荷3を接続するとともに、NチャンネルFET1のドレインに正極性電源、NチャンネルFET2のソースに負極性電源を接続したものであって、NチャンネルFET1のソースとNチャンネルFET2のドレインの接続点の負荷3への出力を基準として、NチャンネルFET1のゲートを制御する第1の駆動回路17と、負極性電源を基準として、NチャンネルFET2のゲートを制御する第2の駆動回路18を有する。

(もっと読む)

高出力パワーアンプ

【課題】高出力パワーアンプにおいて、主基板の反りによる放熱悪化により、電流増や高周波特性劣化が発生してしまうことを抑制し、且つ、半導体の特性を最大限に引き出すことを可能とする高出力パワーアンプの提供を課題とする。

【解決手段】本発明の高出力パワーアンプ20は、Push-Pull構成の半導体信号線間に、両面若しくは片面に積層銅張り層21,22が設けられ、且つネジ孔23が設けられた整合用小型基板11が、ネジ12によって主基板4に押し付けられて取り付けられ、これにより、主基板4の反り防止と、半導体直近における整合回路の形成とを両立できる。

(もっと読む)

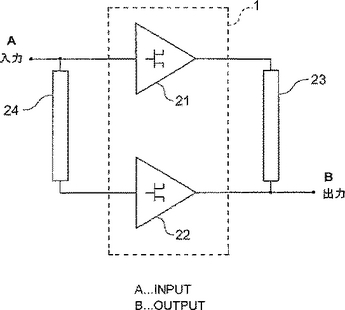

プッシュプル増幅器

【課題】 差動増幅器で発生するオフセットの影響を排除でき、収率に優れかつ低消費電流で大電流駆動能力を有したプッシュプル増幅器の提供

【解決手段】この発明は、差動増幅器1と、差動増幅器2と、P型のMOSトランジスタ3およびN型のMOSトランジスタ4からなる出力増幅部15と、オフセット制御部17とを備えている。差動増幅器1は、オフセット電圧を調整するためのオフセット調整端子10を有する。オフセット制御部17は、差動増幅器1と差動増幅器2の出力電位差を基準電圧になるように制御するものであり、差動増幅器1の出力電圧と差動増幅器2の出力電圧との減算を行う減算回路11と、減算回路11の出力電圧と基準電圧Vrefとの減算を行う減算回路13と、減算回路13の出力電圧を増幅する増幅回路14とを備え、増幅回路14の出力を差動増幅器1のオフセット調整端子10に供給するようになっている。

(もっと読む)

自動ゲイン補正を有する増幅器回路

本発明は、増幅器の回路およびシステムに関し、ブリッジ構成における第1および第2の増幅器手段(22、24)を有する相補形増幅器段中において生成されるゲイン・アンバランスを補償する方法に関する。補償オフセット電流が、前記第1および第2の増幅器手段のそれぞれの入力に供給される入力信号のこれらの値に応じて生成され、この補償オフセット電流は、これらの第1および第2の増幅器手段(22、24)のこれらの入力の間のジャンクション・ノードに注入される。それによって、これらの第1および第2の増幅器手段のゲインは、入力信号の種類、すなわち平衡入力信号または不平衡入力信号には依存しないことが保証される可能性がある。このようにして自動ゲイン補正が、達成される可能性があり、この増幅器回路の入力源または入力構成の種類に依存するゲイン制御回路の選択のための追加の制御信号または制御端子の要件は、削除されてもよい。  (もっと読む)

(もっと読む)

61 - 70 / 72

[ Back to top ]