国際特許分類[H03F3/45]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 増幅器 (10,074) | 増幅素子として電子管のみまたは半導体装置のみをもつ増幅器 (6,434) | 差動増幅器 (968)

国際特許分類[H03F3/45]に分類される特許

31 - 40 / 968

演算増幅器

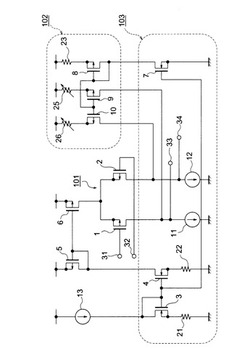

【課題】入力オフセット電圧温度変動を悪化させることなく入力オフセット電圧のゼロ調整を可能とする。

【解決手段】差動対をなすように第1及び第2のPチャネルMOSトランジスタ1,2が差動接続されてなる差動増幅回路101を有すると共に、第1及び第2のPチャネルMOSトランジスタ1,2へテール電流を供給する第3の定電流源13に対して負の温度特性を有する電流を生成、出力する負温度特性電流生成回路103と、第1及び第2のPチャネルMOSトランジスタ1,2の各々へ入力オフセット電圧補正電流を供給する入力オフセット電圧補正電流生成回路102とを具備し、入力オフセット電圧補正電流生成回路102は、負温度特性電流生成回路103の出力電流を基に、入力オフセット電圧補正電流を出力調整可能に構成されたものとなっている。

(もっと読む)

増幅器

【課題】増幅器の出力雑音電圧を抑制する。

【解決手段】正転入力電圧と反転入力電圧の差分を増幅する差動入力回路1と、差動入力回路1の出力信号を増幅して出力端子に出力する出力回路2と、差動入力回路1の電流源MP3と出力回路2の電流源MP4にバイアス電圧を出力するバイアス回路5を備えた増幅器である。差動入力回路1の正転入力電圧と反転入力電圧が共に接地電圧のときに出力端子に現れる出力雑音電圧を検出し、該雑音電圧のレベルが高いほど、バイアス回路5が、電流源MP3,MP4の電流を増大させるバイアス電圧を出力するようにした。

(もっと読む)

電力分配回路

【課題】差動入力信号を入力し1対の差動出力信号を出力する際、差動出力信号間の回路誤差を低減する。

【解決手段】電力分配回路10はトランス2A、2B及び加算回路3を含む構成である。トランス2Aの出力信号は、正相信号(Vout2Ap)の位相θ1+90°、逆相信号(Vout2An)の位相θ1−90°の差動信号として出力される。トランス2Bの出力信号は、正相信号(Vout2Bp)の位相θ2+90°、逆相信号(Vout2Bn)の位相θ2−90°の差動信号として出力される。加算回路3は、トランス2A,2Bからの2対の差動信号を、正相信号及び逆相信号毎にベクトル加算し、1対の差動出力信号に合成する。差動出力信号は、トランス2A,2Bにおいて生じた位相誤差(θ1−θ2)が補正された信号として得られる。

(もっと読む)

増幅器、液晶表示用駆動回路、及び液晶表示装置

【課題】 入力段及び出力段の電源電位にかかわらず、増幅器の電力消費を抑えつつスルーレートを向上する。

【解決手段】 増幅器は、差動入力端子及び出力端子を有し、前記出力端子が前記差動入力端子の一方に帰還され、前記差動入力端子の他方に入力される入力信号を増幅し前記出力端子から出力するボルテージフォロア回路と、前記ボルテージフォロア回路に所定の電流を供給する第1電流源と、前記差動入力端子の他方と前記出力端子との間の電位差が所定値以上である場合に前記ボルテージフォロア回路に電流を供給する第2電流源と、を備える。

(もっと読む)

ボルテージフォロワ回路

【課題】動作電流を大きく増大させることなく、入力信号変化に対する出力追従性を向上させることのできるボルテージフォロワ回路を提供する。

【解決手段】実施形態のボルテージフォロワ回路は、P型差動対101と、N型差動対102と、折り返しカスコード型中間増幅段103と、出力段104とを備える演算増幅回路100を使用するボルテージフォロワ回路であって、出力変化加速部1が、P型差動対101に接続された定電流源I101からP型差動対101へ電流が流れないときに、出力段104へ加速電流I1を印加して出力段104の出力変化を加速し、出力変化加速部2が、N型差動対102に接続された定電流源I102からN型差動対102へ電流が流れないときに、出力段104へ加速電流I2を印加して出力段104の出力変化を加速する。

(もっと読む)

半導体装置

【課題】消費電流を削減する。

【解決手段】第1及び第2の入力端子に現れる電位差を第1及び第2の電源に基づいて増幅する差動アンプ(図2のMN1、MN2が相当)と、差動アンプを動作させるバイアス電流を制御するバイアストランジスタ(図2のMN3が相当)と、差動アンプの負荷となるカレントミラー回路(図2のMP1、MP2が相当)と、カレントミラー回路のダイオード接続側と其々の制御端が接続されると共に第1及び第2の電源間に直列に接続される、バイアストランジスタと逆導電型の第1及び第2のトランジスタ(図2のMP4、MP6が相当)を有し、第1及び第2のトランジスタの間の接続ノードをバイアストランジスタの制御端に接続するバイアス制御回路と、を備える。

(もっと読む)

オペアンプ

【課題】位相余裕を減らすことなく電源立ち上げ時における出力電圧の立ち上がりを速くする。

【解決手段】電源電圧が立ち上がると、入力電圧VinpがVinmよりも高くなるので、トランジスタ9がオン、トランジスタ10がオフとなり、差動対11に供給される動作電流は全てトランジスタ9に流れる。電流検出回路62に電流が流れないので、トランジスタ73がオフし、第2の定電流回路69が出力する増分動作電流I2は、ダイオード72を通して差動対11に流れ込む。トランジスタ9に流れる電流は定常動作電流I1+増分動作電流I2となり、位相補償コンデンサ8の充電電流が増えて出力電圧Voの立ち上がりが速くなる。

(もっと読む)

差動増幅回路及びコンパレータ

【課題】オフセット電圧の変動を低減した差動増幅回路及びコンパレータを提供する。

【解決手段】実施形態によれば、差動回路と、出力回路と、クリップ回路と、を備えたことを特徴とする差動増幅回路が提供される。前記差動回路は、一対の入力信号の電位差に応じた一対の差動電流を生成する。前記出力回路は、前記一対の差動電流を受けて、電流差に応じた出力電圧を生成する。前記クリップ回路は、前記出力電圧に応じてオンし、前記出力電圧をしきい値電圧を含みローレベルまたは前記ローレベルよりも高いハイレベルに変換できる範囲に抑制するクリップ素子を有する。

(もっと読む)

バイアス回路

【課題】動作トランジスタのエミッタ電圧の温度依存性を抑制する。

【解決手段】動作トランジスタQ8にベースには、バイアス電流Ibが第1抵抗R3,R4、第1トランジスタQ7を介し供給される。少なくとも1つのカレントミラー回路を含み、バイアス電流Ibに応じた対応電流Ib’が第2トランジスタQ3に流れる。第3トランジスタQ2は、第1トランジスタとベースが共通接続され、対応電流Ib’を流し、第2抵抗R2は、前記第1抵抗R3における電圧降下に対応する電圧降下を得る。第4トランジスタQ1はエミッタ側に基準電圧Vrefを受け、ベースが前記第3トランジスタQ2のエミッタ側に接続される。動作トランジスタQ8の1VBEを第4トランジスタQ1の1VBEで相殺し、第2トランジスタQ7の1VBEを前記第3トランジスタQ2の1VBEで相殺することによって、基準電圧Vrefを動作トランジスタQ8のエミッタ側に設定する。

(もっと読む)

電力増幅器、及び、電子装置

【課題】

出力の線形性を改善した電力増幅器、及び、電子装置を提供する。

【解決手段】

電力増幅器は、所望波が差動入力される一対の第1増幅部と、前記第1増幅部の出力側に接続される一対の第2増幅部と、前記第2増幅部の出力側に接続されるトランスと、電源から前記第1増幅部に電力を供給するとともに、前記トランスを介して前記第2増幅部に電力を供給する電力供給線と、前記第1増幅部と前記第2増幅部との間に接続され、前記所望波を前記第2増幅部に通過させるとともに、前記所望波の二次歪み成分を遮断する遮断回路とを含む。

(もっと読む)

31 - 40 / 968

[ Back to top ]