国際特許分類[H03F3/45]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 増幅器 (10,074) | 増幅素子として電子管のみまたは半導体装置のみをもつ増幅器 (6,434) | 差動増幅器 (968)

国際特許分類[H03F3/45]に分類される特許

61 - 70 / 968

分布定数型増幅器

【課題】分布定数型差動増幅器の出力波形におけるジッタを低減する。

【解決手段】分布定数型増幅器は、複数の増幅器を有する。複数の増幅器はそれぞれ、固有の遅延時間を持って一の信号源からの入力信号を受ける。また、複数の増幅器はそれぞれ、固有の遅延時間に対応する遅延時間をもって共通の負荷に出力信号を提供する。複数の増幅器それぞれに関して、固有の遅延時間と対応する遅延時間の和は等しく設定されている。複数の増幅器のそれぞれは、一対の差動トランジスタと、該一対の差動トランジスタと当該増幅器の出力との間に直列に挿入された一対のカスコードトランジスタを含む。一対の差動トランジスタは、当該一対の差動トランジスタそれぞれのコレクタ−ベース間の接合容量が準飽和領域の接合容量となるように、バイアスされている。

(もっと読む)

差動増幅回路

【課題】チップ面積を小さくする。

【解決手段】一端がグランド端子14に接続される定電流源13と、ソースが共通に定電流源13の他端に接続され、ゲートが入力端子A、Bにそれぞれ接続される第1および第2の差動対(Q11、Q12およびQ13、Q14に相当)と、第1の差動対のそれぞれのドレインにそれぞれのソースを接続するnMOSトランジスタQ15、Q16と、nMOSトランジスタQ15、Q16のそれぞれのドレインを出力端子C、Dとし、出力端子C、Dと電源端子11との間に接続される負荷部(図1のQ17、Q18に相当)と、を備え、第1の差動対のそれぞれのドレインを第2の差動対の逆相となるそれぞれのドレインに接続し、nMOSトランジスタQ15、Q16のそれぞれのゲートは、nMOSトランジスタQ15、Q16のドレインにそれぞれ接続する。

(もっと読む)

オフセット調整差動増幅回路

【課題】オフセット調整差動増幅回路において、オフセット調整値を温度に対して安定して維持することを提供する。

【解決手段】オフセット調整差動増幅回路は、差動対を構成する第1、第2のMOSトランジスタM1、M2と、第1のMOSトランジスタM1のソースに一端が接続される第1の抵抗R1と、第2のMOSトランジスタM2のソースに一端が接続され、第1の抵抗R1の他端に他端が接続される第2の抵抗R2と、第1、第2の抵抗R1、R2の接続点と第1の電源端子との間に接続され、差動対の動作電流を供給する電流源M6と、第1のMOSトランジスタM1のソースにソースが接続され、第2の電源端子にドレインが接続され、ゲートにオフセット調整電圧VTが与えられ、第1の抵抗R1の両端に生じる電圧を調節するオフセット調整電流I7をオフセット調整電圧VTに応じて制御する第3のMOSトランジスタM7と、を有する。

(もっと読む)

差動増幅器及びアナログ/デジタル変換器

【課題】スイッチに流れるオフリーク電流の影響を抑制し、利得の発振を抑える。

【解決手段】差動増幅器16は、入力信号が入力される入力端子27,28と、前記入力信号が増幅された出力信号を出力する出力端子25,26と、を備える差動増幅器16であって、前記入力信号を増幅し前記出力信号を生成する増幅部21と、前記増幅部21と電源端子との間に接続され、第1導電型トランジスタT34,T35と、前記第1導電型トランジスタT34,T35のゲート端子をドレイン端子に接続するかまたは前記出力端子25,26に接続するかを切り替える切り替えスイッチ22と、を有する負荷回路23と、前記切り替えスイッチ22のオフリーク電流を低減するキャンセル電流を生成するリークキャンセルスイッチ30と、を備える。

(もっと読む)

増幅回路

【課題】動作電流を減少させることが可能となり、低消費電力化が可能となる増幅回路の提供。

【解決手段】この発明は、差動対を構成し、互いに逆相の差動入力信号vipx、vinxが入力されるMOSトランジスM1、M2と、MOSトランジスタM1、M2のそれぞれの負荷となるMOSトランジスタM3、M4とを備えている。また、MOSトランジスタM3のバルクには、抵抗R5を介してバイアス電圧が印加されるととともに、キャパシタC3を介して反転出力信号vonが入力される。さらに、MOSトランジスタM4のバルクには、抵抗R6を介してバイアス電圧が印加されるととともに、キャパシタC4を介して出力信号vopが入力される。

(もっと読む)

差動増幅回路及び集積回路装置

【課題】差動対を構成する2つのPMOSトランジスターにおけるNBTIの発生を可能な限り防ぐことにより出力オフセット電圧の発生を抑制可能な差動増幅回路及び集積回路装置を提供すること。

【解決手段】差動増幅回路1は、第1の信号が入力されるPMOSトランジスター10(第1のPMOSトランジスターの一例)と、第2の信号が入力されるPMOSトランジスター20(第2のPMOSトランジスターの一例)と、制御信号XSTBに基づいて、PMOSトランジスター10のゲートとバックゲートを同電位にするか否かを選択するPMOSトランジスター14(第1のスイッチ部の一例)と、制御信号XSTBに基づいて、PMOSトランジスター20のゲートとバックゲートを同電位にするか否かを選択するPMOSトランジスター24(第2のスイッチ部の一例)と、を含む。

(もっと読む)

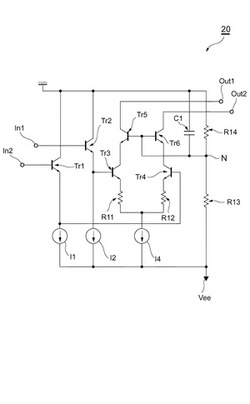

差動増幅器

【課題】差動増幅回路、カレントミラー回路およびレール・トゥ・レール回路を組み合わせた電気回路において、外部からの信号に応じて容量の充放電を高速化する機能を維持しつつ、容量の充放電に寄与しない無駄な電流を減少させた差動増幅器を提供する。

【解決手段】外部からの信号に基づくデジタル信号を生成する論理回路を内蔵するスイッチ制御回路を設けて、容量の充放電を高速化するスイッチをこのデジタル信号を用いて制御する。

(もっと読む)

トランスコンダクタンス調整回路、回路装置及び電子機器

【課題】トランスコンダクタンスを精度良く調整することができるトランスコンダクタンス調整回路、回路装置及び電子機器等を提供すること。

【解決手段】トランスコンダクタンス調整回路100は、第1の信号I及び第1の信号Iと位相が90度異なる第2の信号Qが入力され、第1、第2の抵抗素子RA1と、第1、第2のキャパシターCA1、CA2と、演算トランスコンダクタンス増幅器で構成される中心周波数シフト回路110と、トランスコンダクタンス調整信号AGMを出力する調整信号生成回路120とを含む。調整信号生成回路120は、第2の信号Qと第1の出力信号OIとに基づいて、又は第1の信号Iと第2の出力信号OQとに基づいて、又は第1の信号Iと第1の出力信号OIとに基づいて、又は第2の信号Qと第2の出力信号OQとに基づいて、トランスコンダクタンス調整信号AGMを生成する。

(もっと読む)

差動信号発生回路および電圧制御ゲイン可変増幅器

【課題】電圧制御によりゲイン調整を行うゲイン可変増幅器制御用の制御電圧を、基準電圧を用いることなく生成し、電圧制御ゲイン可変増幅器全体の小型化および消費電力の削減を図る。

【解決手段】ゲイン可変増幅器制御回路を構成する差動対として、nチャネル型トランジスタTR11とpチャネル型トランジスタTR12とを用い、共通のゲイン制御電圧S1をこれらトランジスタTR11およびTR12のゲートに供給する。各トランジスタTR11、TR12を流れる電流は、ゲイン制御電圧S1が増加するにつれて一方は増加し、他方は減少する特性となり、基準電圧を用いたゲイン可変増幅器制御回路と同一特性のゲイン可変増幅器制御電圧を得ることができる。よって、基準電圧発生回路を設ける必要がないため、装置全体の小型化および消費電力の削減を図ることができる。

(もっと読む)

チャージアンプ

【課題】帰還抵抗の寄生容量による悪影響をなくして、半導体基板上で実用化が可能な、出力ノイズの小さいチャージアンプを提供する。

【課題の解決手段】チャージアンプ1は、非反転入力端子を増幅基準電圧6に接続し、反転入力端子に水晶振動子を有する振動型角速度センサ7から50KHzの周波数信号を入力するとともに、その出力端子は並列接続された帰還抵抗4,5及び帰還容量3を介して反転入力端子に接続したものであって、帰還抵抗4,5の反転入力端子側ほぼ半分に対応する寄生容量8の基板電極を反転入力端子に接続して、出力ノイズを低減したものである。

(もっと読む)

61 - 70 / 968

[ Back to top ]