国際特許分類[H03F3/45]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 増幅器 (10,074) | 増幅素子として電子管のみまたは半導体装置のみをもつ増幅器 (6,434) | 差動増幅器 (968)

国際特許分類[H03F3/45]に分類される特許

41 - 50 / 968

完全差動型オペアンプ

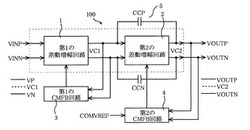

【課題】完全差動型オペアンプの動作の安定度を向上し、高速動作を可能にする。

【解決手段】差動増幅部は、第1ステージの第1の差動増幅回路と、第2ステージの第2の差動増幅回路2から構成される。位相補償回路5は、第2の差動増幅回路2の差動入力端子と差動出力端子との間に接続されている。第1のCMFB回路3は、第1ステージの差動増幅回路1の差動出力電圧VP,VNの第1の同相電圧VC1が第1の基準電圧になるように、第1の差動増幅回路1をフィードバック制御する。第2のCMFB回路4は、第2の差動増幅回路2の差動出力電圧VOUTP,VOUTNの第2の同相電圧VC2が第2の基準電圧になるように、第2の差動増幅回路2をフィードバック制御する。

(もっと読む)

レールツーレールDMOS増幅器の出力ステージにバイアスをかけるための方法及び装置

【課題】レールツーレールDMOS増幅器の出力ステージにバイアスをかけるための方法及び装置を提供する。

【解決手段】本願発明は、増幅器であって、入力信号を受け取るための入力ステージと、前記入力ステージに連結されると共に、前記入力信号に応答して出力ドライバステージに対して駆動信号を提供する高利得ステージと、前記出力ドライバステージに連結された出力端子とを具備することを特徴とする。前記出力ドライバステージは、前記高利得ステージから第1の駆動信号“pdrive”を受け取る第1の端子、第1の電圧降下を通じてVDDに連結された第2の端子、及び、前記増幅器の前記出力端子に連結された第3の端子を有する高電位側ドライバ回路を備える。

(もっと読む)

半導体集積回路

【課題】効果的に雑音レベルを低減した半導体集積回路を提供する。

【解決手段】差動入力トランジスタであるPチャネル型MOSトランジスタM1,M2は、雑音レベルを低減するために薄いゲート酸化膜を有している。これらのPチャネル型MOSトランジスタM1,M2を過電圧から保護する保護回路は、Pチャネル型MOSトランジスタM3,M4を含んで構成されている。Pチャネル型MOSトランジスタM3はPチャネル型MOSトランジスタM1を過電圧から保護する第1の保護トランジスタであり、Pチャネル型MOSトランジスタM1のドレイン側に直列に接続されている。Pチャネル型MOSトランジスタM4は、Pチャネル型MOSトランジスタM2を過電圧から保護する第2の保護トランジスタであり、Pチャネル型MOSトランジスタM2のドレイン側に直列に接続されている。

(もっと読む)

差動トランスインピーダンス増幅器

【課題】同相入力電流成分に対する耐性を大きくする。

【解決手段】差動トランスインピーダンス増幅器は、入力信号合成回路12で得られた、入力端子IT,ICのそれぞれの信号を合成した同相入力電圧と、出力信号合成回路15で得られた、出力端子OT,OCのそれぞれの信号を合成した参照電圧との差電圧に応じた制御信号を制御用増幅器13で生成し、可変電流源IS1,IS2で、この制御信号に応じた量の電流を入力電流信号から引き抜く。入力信号合成回路12は、抵抗R31〜R33と、容量C31とから構成される。出力信号合成回路15は、抵抗R41〜R43と、容量C41とから構成される。

(もっと読む)

半導体装置

【課題】消費電力が低減された半導体装置を提供することである。

【解決手段】入力電位および基準電位が入力される差動増幅器、利得段および出力電位が出力される出力段を有する半導体装置において、該出力段にオフ状態でのリーク電流が低いトランジスタを配置することで、該利得段から供給される電位が一定に保持される半導体装置である。また、オフ状態でのリーク電流が低いトランジスタとしては、酸化物半導体層を有し、且つ酸化物半導体層にチャネル形成領域を有するトランジスタを用いることである。

(もっと読む)

受信機および高周波増幅器

【課題】高周波増幅器の消費電流の増加を伴うことなく、良好なNFを得ることのできる受信機を提供する。

【解決手段】負荷抵抗としての抵抗R1とこれに直列に接続されたMOSトランジスタM1からなるシングル増幅回路1と、MOSトランジスタM2およびM3からなる差動対を有する差動増幅回路2とから高周波増幅器10を構成する。MOSトランジスタM1のゲートに増幅対象の信号を入力し、シングル増幅回路1の出力をDCバイアスカット用のキャパシタC1を介して差動増幅回路2の差動対の一方のMOSトランジスタM2のゲートに入力し、他方のMOSトランジスタM3は無入力とする。MOSトランジスタM2およびM3からなる差動対の出力信号を、高周波増幅器10の出力信号として出力する。高周波増幅器10のNFが改善されるため受信機100のNFが改善されることになる。

(もっと読む)

適応型バイアシングを用いた高スイング演算増幅器出力段

【課題】加工コストを増大させず、適応型バイアシング出力段を用いた高スイング演算増幅器を提供する。

【解決手段】出力段123は、VDDAノードと出力ノードとの間のプルアップ電流経路内において直列に結合された2つのトランジスタ(スイッチングトランジスタT3及びバイアシングトランジスタT4)を含み、前記出力ノードと接地ノードとの間のプルダウン電流経路内において直列に結合された2つのトランジスタ(スイッチングトランジスタT1及びバイアシングトランジスタT2)も含む。前記バイアシングトランジスタT4,T2を提供することは、前記トランジスタT3,T4において低下される最大電圧を低減させ、それによって前記トランジスタT1〜T4がVDDAよりも低い破壊電圧を有するのを可能にする。

(もっと読む)

半導体装置

【課題】シングルエンド−差動変換器を備えた半導体装置において、理想的な出力差動電流特性が得られる周波数の上限を向上させる。

【解決手段】入力電圧Vinを、パッケージ3の外部電極PIN1に入力し、外部電極PIN1、ボンディングワイヤWire1、チップ2の入力端子PAD1、シングルエンド−差動変換器1の入力端子Tin1を介してゲート接地のMOSトランジスタM1のソースに伝達する。また、外部電極PIN1、ボンディングワイヤWire2、チップ2の入力端子PAD2、シングルエンド−差動変換器1の入力端子Tin2を介してソース接地のMOSトランジスタM2のゲートに伝達する。

(もっと読む)

半導体装置

【課題】レイアウト面積を大きくすることなく、差動対を高速/高消費電流と、低速/低消費電流の両方で動作させることができるようにした半導体装置を提供する。

【解決手段】差動回路5aは、差動対トランジスタN1,N2と、差動対トランジスタN1,N2に流れる電流量が少なくとも2つのレベルで切替わるように、切替可能なテール電流を供給するテール電流源68とを備える。差動対トランジスタN1,N2は、差動対トランジスタN1,N2に流れる電流の減少に伴って、σ(ΔI/gm)の値が単調に減少する特性を有する、ただし、σは標準偏差、ΔIは、差動対トランジスタN1,N2の電流量の差分、gmは、差動対トランジスタN1,N2のトランスコンダクタンスを表わす。

(もっと読む)

増幅回路

【課題】簡易な構成で歪を抑制しつつ消費電流を低減する。

【解決手段】増幅回路100は、正入力端子T1と負入力端子T2とに供給される電圧の差分を増幅し差分電圧Vaを出力する差動増幅部10と、入力信号Vinの電圧を検出し検出電圧Vbを出力する入力電圧検出部20と、正電源電圧+Vccが供給される正電源端子T6と出力端子Toutとの間に設けられ、出力端子Toutから電流を吐き出すPMOS31と、負電源電圧−Vccが供給される負電源端子T7と出力端子Toutとの間に設けられ、出力端子Toutから電流を吸い込むNMOS32とを有する出力部30とを備える。

(もっと読む)

41 - 50 / 968

[ Back to top ]