国際特許分類[H03H17/02]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | インビーダンス回路網,例.共振回路;共振器 (15,336) | ディジタル技術を用いる回路網 (734) | 周波数選択回路網 (514)

国際特許分類[H03H17/02]の下位に属する分類

国際特許分類[H03H17/02]に分類される特許

61 - 70 / 278

動的構成可能ANRフィルタおよび信号処理トポロジー

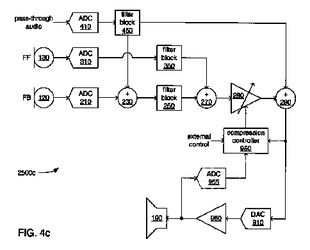

ANR回路、事によってはパーソナルANRデバイスのANR回路には、フィードバックベースANR、フィードフォワードベースANRおよびパススルーオーディオの準備をサポートするための信号処理トポロジーが組み込まれており、トポロジーには、フィードバックマイクロフォンから受け取ったフィードバック基準音響からフィードバック対雑音音響が生成される分岐、フィードフォワード基準音響からフィードフォワード対雑音音響が生成される分岐、および音響源から受け取ったパススルーオーディオ音響から修正パススルーオーディオ音響が生成される分岐が組み込まれており、これらの3つの分岐は、生成された個々の分岐の音響を単一の出力に結合するべく結合されており、この単一の出力によって音響ドライバ、事によってはパーソナルANRデバイスの音響ドライバが駆動される。これらの通路の各々に対して、個々の通路の相互接続、個々のフィルタの係数、任意のVGAの利得設定のためのANR設定を、さらに他のANR設定と共に動的に構成することができ、この動的構成は、これらの通路のうちの1つまたは複数に沿った一片または複数片のデジタルデータの転送と同期して実施される。  (もっと読む)

(もっと読む)

低電力のプログラム可能なデジタルフィルタ

【課題】通信システムのトランシーバにより使用されるように構成された、入力周波数の範囲またはサンプルレートを適合させることのできるスペース効率のよい低電力のプログラム可能なデジタルフィルタを提供する。

【解決手段】入力信号を受信し、第1の伝達関数を有する第1の有限インパルス応答フィルタセクション16と、第2の伝達関数を有する、第1の有限インパルス応答フィルタセクション16に接続された無限インパルス応答フィルタセクション18と、無限インパルス応答フィルタセクション18に接続され、プログラム可能なデジタルフィルタによる入力信号の受信に応答して濾波された出力信号を出力し、第3の伝達関数を有する第2の有限インパルス応答フィルタセクション20と、第1、第2または第3の伝達関数におけるプログラム可能な係数を供給する手段とを具備する。

(もっと読む)

帯域分割フィルターおよびプログラム

【課題】少ない演算量で、かつ所望の周波数特性を確保しながら、信号を高域と低域とに分割することのできる帯域分割フィルターを提供する。

【解決手段】入力信号を1サンプルずつ遅延させる遅延器1−1〜1−mと、遅延器1−1〜1−mのそれぞれの入出力に得られる遅延量の異なる信号にそれぞれ係数を乗算する乗算器2−0〜2−mと、乗算器2−0〜2−mの出力を加算して第1のフィルター出力とする加算器3、4と、遅延器1−1〜1−mのそれぞれの入出力のうち遅延量が中央値となる信号に、対応する乗算器2−(m/2)の係数am/2を1から減算した値を係数として乗算した値と、中央値となる信号以外の遅延器1−1〜1−mのそれぞれの入出力に、対応する乗算器の係数の逆符号の値を係数として乗算した値との和を生成して第2のフィルター出力とする乗算器5、6および加算器7とを有する。

(もっと読む)

適応等化器および適応等化方法

【課題】低コストで処理遅延の短い適応等化器を得る。

【解決手段】適応等化器100において、第1のサンプリング周波数は第2のサンプリング数より高い値に設定する。第1および第2の入力信号は、第1および第2のA/D変換部101,102によって第1のサンプリング周波数でA/D変換され、第1および第2のSRC部103によって第2のサンプリング周波数にサンプリング変換される。適応化学習処理部107が第2のサンプリング周波数で適応フィルタ係数列の学習同定を行い、係数変換処理部109が適応フィルタ係数列を第1のサンプリング周波数用に変換する。フィルタ処理部110がこの適応フィルタ係数列を用いて、第1のサンプリング周波数で第1の入力信号をフィルタリングして出力信号を生成する。

(もっと読む)

くし型フィルタ

【課題】 ピーク部の振幅特性とディップ部の振幅特性を夫々独立に制御することが可能なくし型フィルタを提供する。

【解決手段】 基本周波数(ピッチ)及びその高調波を強調するくし型フィルタ1であって、入力信号を所定時間遅延させて遅延信号を出力する遅延手段2と、この遅延手段2の遅延信号と入力信号を加算して加算信号を出力する第1加算手段3と、入力信号から遅延信号を減算して減算信号を出力する減算手段4と、加算信号に定数αを乗算して出力する第1乗算手段5と、減算信号に定数βを乗算して出力する第2乗算手段6と、第1乗算手段5の出力信号と第2乗算手段6の出力信号を加算して出力する第2加算手段7と、この第2加算手段7の出力信号に0.5を乗算して出力する第3乗算手段8からなる。

(もっと読む)

オーディオ信号処理回路、フィルタ回路およびそれを用いたオーディオシステム

【課題】フィルタの特性を短時間で切りかえる。

【解決手段】IIR(無限インパルス応答)フィルタ10は、デジタルの入力オーディオ信号Sinに対して、設定された係数COEFFに応じたフィルタリング処理を施す。RAM20は、フィルタ10の係数COEFFを格納する。インタフェース回路30は、外部のプロセッサ202から、フィルタ10の特性を示すパラメータデータPRMを受ける。演算部50は、インタフェース回路30が受けたパラメータデータPRMにもとづき、フィルタ10の係数COEFFを計算し、演算部50に格納する。

(もっと読む)

フィルタリング装置、フィルタリング方法、プログラムおよびサラウンドプロセッサ

【課題】長さNの離散時間信号x[n]と長さMのフィルタ係数h[m]の畳み込み演算の演算量等を低減する。

【解決手段】N,Mは、M-1≦(P-N)/2を満足する。離散時間信号x[n]を、x1[n],x2[n]に分割し、x1[n]の長さをP/2-(M-1)、x2[n]の長さを残りの長さとし、x1[n]及びx2[n]にゼロ詰めをして、長さP/2、Qのゼロ詰めデータx1′[n],x2′[n]を得る。Qは、N2+M-1以上の最小の2の乗数である。h[m]にゼロ詰めをして、x1′[n],x2′[n]に対応したゼロ詰めデータh1′[n],h2′[n]を得る。各ゼロ詰めデータにFFTを行い、周波数領域で乗算し、その乗算結果に対してIFFTを行って、2つの離散時間信号y1[n],y2[n]を得て、重複加算法で加算して、出力離散時間信号y[n]を得る。Q≦P/2となるため、非分割方式より、演算量等を低減できる。

(もっと読む)

デジタル信号処理装置

【課題】フィルタ係数を格納するメモリへアクセスする際に生じる電力消費量を低減する。

【解決手段】複数のフィルタ係数を複数ビット毎に分割データとして分割記憶する部分メモリに分割され、入力されるアドレスに対応するフィルタ係数の各分割データを各部分メモリからそれぞれ出力する係数格納用メモリ2と、チップイネーブル(CE)信号を各部分メモリに伝達するか遮断するかを部分メモリ毎に指定する活性化/非活性化制御情報を付加したアドレス信号を係数格納用メモリに出力する制御部1と、活性化/非活性化制御情報に基づいて各部分メモリに対してCE信号を伝達/遮断するCE信号遮断部3と、複数の部分メモリの少なくとも一部に設けられ、活性化/非活性化制御情報に基づき、部分メモリの出力と全ビットゼロ値との何れかを選択出力する出力選択部4と、を備える。

(もっと読む)

サンプリング周波数変換装置

【課題】サンプリング周波数変換装置に関し、変換するサンプリング周波数の比が簡単な整数比でない場合や、サンプリング周波数の揺らぎに対して、出力側のサンプリング周波数のみに同期して、周波数変換後の離散信号を出力する。

【解決手段】第1のサンプリング周波数の離散信号データを、該第1のサンプリング周波数のクロックで取り込んでラッチする第1のラッチ部1−1と、第1のラッチ回路1−1から出力される離散信号データを、第2のサンプリング周波数の整数倍の周波数のクロックで取り込んで出力するオーバサンプリング同期部1−2と、オーバサンプリング同期部1−2の出力信号の低域成分を通過させるデジタルフィルタ1−3と、デジタルフィルタ1−3から出力される信号を、第2のサンプリング周波数のクロック毎に間引いて出力するデシメーション部1−4を備える。

(もっと読む)

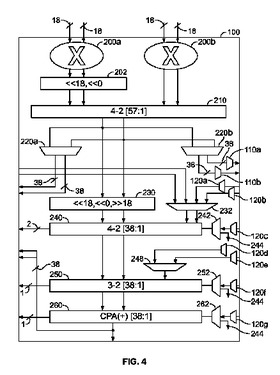

回路のモジュール間に選択的に使用可能な専用連結を有するモジュール式デジタル信号処理回路

所望の場合に、より大きな(例えば、より複雑および/またはより演算上正確な)DSP演算を行うように、より簡単に連動することができるデジタル信号処理(「DSP」)回路ブロックを提供する。これらのDSPブロックはまた、あるブロックを使用できないにもかかわらず(例えば、回路欠陥のために)、複数のそのようなブロックをつなぎ合わせることを容易にする冗長回路を含んでもよい。シストリックレジスタが、シストリック型の有限インパルス応答(「FIR」)デジタルフィルタを実装するよう、ブロックの使用を容易にするために、DSPブロックの中の種々のポイントに含まれてもよい。  (もっと読む)

(もっと読む)

61 - 70 / 278

[ Back to top ]