国際特許分類[H03K17/687]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 特定の構成要素の使用によって特徴づけられたもの (2,578) | 能動素子として半導体装置を用いるもの (2,114) | 装置が電界効果トランジスタであるもの (1,712)

国際特許分類[H03K17/687]の下位に属する分類

制御回路と出力回路の間が電気的に絶縁されたもの

いくつかの入力または出力端子をもつスイッチング装置,例.マルチプレクサ,分配器 (320)

誘導性負荷をもつもの (196)

国際特許分類[H03K17/687]に分類される特許

61 - 70 / 1,196

半導体装置

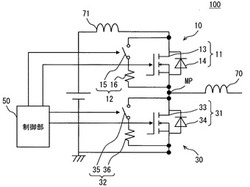

【課題】体格及びコストの増大が抑制された半導体装置を提供する。

【解決手段】直流電源とグランドとの間に直列接続された2つの単位回路と、単位回路を制御する制御部と、を備え、2つの単位回路の中点に誘導性負荷が接続された半導体装置であって、2つの単位回路それぞれは、第1スイッチ素子と、第1スイッチ素子と逆並列接続された還流ダイオードと、還流ダイオードと第1スイッチ素子それぞれと並列接続されたバイパス部と、を有し、バイパス部は、直列接続された第2スイッチ素子及び抵抗を有し、制御部は、2つの単位回路の第1スイッチ素子をOFF状態にするデッド期間を挟んで、2つの第1スイッチ素子を交互にON状態とし、デッド期間において、一方の第1スイッチ素子がOFF状態からON状態に移行するまで、一方の第1スイッチ素子と並列接続された第2スイッチ素子をON状態にする。

(もっと読む)

電流駆動型半導体スイッチの駆動回路

【課題】従来の電流駆動型半導体スイッチ8の駆動回路は、駆動回路における電力損失を抑制するためにスイッチやスイッチを制御するための手段が必要となり部品点数が増える。

【解決手段】電源1と電流駆動型半導体スイッチ8のベース又はゲート端子の間に接続される負の温度特性を有する第1の可変抵抗10と、前記電流駆動型半導体スイッチ8のコレクタ又はドレイン電流による動作損失により過熱される熱伝導部11を備え、前記第1の可変抵抗10を前記熱伝導部11により熱が供給されるように配置する。

本発明により、簡単な構成で部品点数を増やすことなく駆動回路における電力損失を抑制することができる。

(もっと読む)

負荷駆動回路

【課題】簡単な構成で負荷オープン状態を検出することができる負荷駆動回路を提供する。

【解決手段】電源端子T1に入力される入力電圧Vinよりも低い基準電圧V1と出力端子T2の電圧Voutとを比較する第1のコンパレータ8と、スイッチング素子2がオフ状態で、且つ負荷オープン状態である場合に、出力端子T2の電圧Voutを基準電圧V1よりも高く、且つ入力電圧Vinよりも低いclamp電圧にクランプするクランプ回路7とを備えることにより、第1のコンパレータの出力によって、負荷オープン状態を検出する。また、入力電圧Vinよりも低く且つclamp電圧よりも高い基準電圧V2と出力端子T2の電圧Voutとを比較する第2のコンパレータ9を備えることにより、第1のコンパレータ及び第2のコンパレータ9の出力によって、負荷オープン状態と出力天絡状態とを検出する。

(もっと読む)

ゲートドライブ回路

【課題】オンデューティが50%以上のパルス信号でもスイッチング素子のゲートをドライブできる安価なゲートドライブ回路。

【解決手段】直流電源Vcc1の両端にトーテムポール接続され且つ各ベースにパルス信号が入力されるトランジスタQ2,Q3と、直流電源Vcc2の両端にトーテムポール接続され且つ各エミッタがスイッチング素子Q1のゲートに接続されるトランジスタQ4,Q5と、一次巻線P1がトランジスタQ2,Q3の各エミッタとトランジスタQ2,Q3の一方のコレクタとにコンデンサC1を介して接続され、二次巻線S1がトランジスタQ4,Q5の各ベースとトランジスタQ4,Q5の各エミッタとに接続されたトランスT1とを有し、パルス信号Vinの最大オンデューティは、トランスT1の一次巻線電圧VpとトランジスタQ4,Q5のベース−エミッタ間順方向電圧とに基づいて決定される。

(もっと読む)

ゲートドライブ回路

【課題】ターンオン時のスイッチング特性が変動せず、電力損失を発生せずにスイッチング素子を安定してターンオンさせることができるゲートドライブ回路。

【解決手段】ドレインとソースとゲートとを有し且つワイドバンドギャップ半導体かなるスイッチグ素子Q1のゲートに制御回路からの制御信号を印加することによりスイッチング素子をオンオフ駆動させるゲートドライブ回路であって、制御回路とスイッチング素子のゲートとの間に接続され、第1のコンデンサC1と第1の抵抗R1とからなる並列回路と、スイッチング素子のゲートとソースとの間に接続され、制御信号のオフ信号に対して遅延させてゲートとソースとの間を短絡する短絡手段S4とを備える。

(もっと読む)

パワーMOSFETの駆動回路およびその素子値決定方法

【課題】パワーMOSFETを高速駆動する場合であっても、寄生インダクタンスに流れる電流の時間変化に応じて発生する電圧に起因したセルフターンオンの発生を防止できるようにしたパワーMOSFETの駆動回路、また、その素子値決定方法を提供する。

【解決手段】制御回路が、駆動回路によってスイッチを駆動制御することで、(2)区間においてスイッチS2HおよびS2Lをオンすると共にその他をオフとし、(3)区間においてスイッチS1LおよびS3Hをオンすると共にその他をオフとする。すると、(2)〜(3)区間にかけて、ハイサイド側のMOSFETのゲートソース間を所定のインピーダンスに切り替えることができ、リカバリー後半に至ったとしてもハイサイド側のMOSFETのゲートソース間電圧Vgs1を閾値電圧Vt未満に抑制できる。

(もっと読む)

半導体装置及びそれを備えた半導体リレー装置

【課題】半導体装置及び半導体リレー装置において、製造コストを抑えつつ、CR積の値を小さくする。

【解決手段】双方向スイッチ1を構成する2つのMOSFETのうち、一方のMOSFET2に、化合物半導体で構成されたユニポーラ型化合物半導体装置を用い、他方のMOSFET3に、シリコンで構成されたSi−MOSFETを用いる。ここで、ユニポーラ型化合物半導体装置の中には、Si−MOSFETよりもCR積の値が小さいものが多く存在する。従って、一方のMOSFET2にユニポーラ型化合物半導体装置を用いたことにより、両方のMOSFET2、3にSi−MOSFETを用いた場合に比べて、装置全体のCR積の値を小さくできる蓋然性が高まる。また、Si−MOSFETよりも製造コストの高いユニポーラ型化合物半導体装置を2つ用いた場合に比べて、製造コストを抑えられる。

(もっと読む)

半導体装置

【課題】InやZnなどを含む酸化物半導体をチャネル領域に用いたトランジスタを、P型トランジスタのように駆動できる半導体装置を提供する。

【解決手段】トランジスタとインバータを有し、インバータの出力はトランジスタのゲートに入力され、トランジスタのチャネル領域はIn、Zn若しくはSnを含む酸化物半導体膜を有し、インバータを構成するトランジスタのチャネル領域はシリコンを有し、インバータにハイ電圧を入力すると、インバータからロー電圧が出力されるとともにトランジスタのゲートにロー電圧が入力されてトランジスタはオフし、インバータにロー電圧を入力すると、インバータからハイ電圧が出力されるとともにトランジスタのゲートにハイ電圧が入力されてトランジスタはオンする半導体装置によって解決する。

(もっと読む)

スイッチング回路

【課題】整数倍の信号成分に起因して、負荷回路やスイッチング素子に余分な電流が流れない電力効率を向上したスイッチング回路を提供する。

【解決手段】スイッチング回路1は、第1端子50a及び第2端子50bを有しており、パルス信号により駆動されて第1端子及び第2端子の導通状態をスイッチするスイッチング素子10と、スイッチング素子の第1端子13に電圧を供給する電源部30と、電源部に並列に接続される負荷回路40と、電源部と負荷回路との接続点Pと、スイッチング素子の第1端子との間に接続され、パルス信号のクロック周波数のN倍(Nは1以上の整数)の周波数において、接続点からスイッチング素子へ流れる電流を抑制する受動回路部50と、受動回路部と接続点との間に接続され、N倍の周波数において共振する共振回路部60と、を備える。

(もっと読む)

ゲートドライブ回路

【課題】ワイドバンドギャップ半導体からなるスイッチング素子の回生動作時の電力損失を抑制し、かつ、安定してターンオン/オフさせることができるゲートドライブ回路。

【解決手段】制御回路とスイッチング素子Q1のゲートとの間に接続され、コンデンサC1と抵抗R1とダイオードD1からなる直列回路と、スイッチング素子のゲートとソースとの間にPNP型トランジスタQ2が抵抗R2を介して接続され、トランジスタQ2のコレクタ・ベース間にダイオードD2が接続され、さらにトランジスタQ2のベースはダイオードD1のアノードに接続され、制御回路からのオフ信号が入力されると、トランジスタの接合電圧とダイオードD2との順方向電圧との差分電圧を残してゲートとソースとの間を短絡する。

(もっと読む)

61 - 70 / 1,196

[ Back to top ]