国際特許分類[H03K17/687]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 特定の構成要素の使用によって特徴づけられたもの (2,578) | 能動素子として半導体装置を用いるもの (2,114) | 装置が電界効果トランジスタであるもの (1,712)

国際特許分類[H03K17/687]の下位に属する分類

制御回路と出力回路の間が電気的に絶縁されたもの

いくつかの入力または出力端子をもつスイッチング装置,例.マルチプレクサ,分配器 (320)

誘導性負荷をもつもの (196)

国際特許分類[H03K17/687]に分類される特許

81 - 90 / 1,196

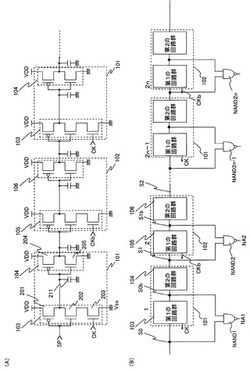

表示装置、表示モジュール及び電子機器

【課題】回路を構成するトランジスタ数を少なくし、且つレベルシフタを配置することな

くシフトレジスタとして正確に動作を行う半導体回路の提供することを課題とする。

【解決手段】第1端子が高電位電源に接続されたpチャネル型トランジスタと、第1端子

が低電位電源に接続されたnチャネル型トランジスタと、を含む回路群と、インバータ回

路と、をm段(mは任意の正の整数であり、m≧3)有し、第2n−1段目(nは任意の

整数であり、m≧2n≧2)の回路群の前記nチャネル型トランジスタのゲートにはクロ

ック信号が入力され、第2n段目(nは任意の整数であり、m≧2n≧2)の回路群の前

記nチャネル型トランジスタのゲートには反転クロック信号が入力される。

(もっと読む)

半導体装置

【課題】耐圧の向上が図られる半導体装置を提供する。

【解決手段】n-型半導体領域には、ドレイン領域となるn-型の拡散領域が形成されている。n-型の拡散領域の周囲を取囲むようにp型の拡散領域が形成されている。p型の拡散領域には、ソース領域となるn+型の拡散領域が形成されている。n-型の拡散領域の直下には、p-型の埋め込み層13が形成されている。n-型の半導体領域の領域には、高電位が印加されるn+型の拡散領域が形成され、そのn+型の拡散領域の表面上には電極が形成されている。電極とドレイン電極とは、配線20によって電気的に接続されている。配線20の直下に位置する部分に、p-埋め込み層13に達するトレンチ3aが形成されて、ポリシリコン膜81が形成されている。

(もっと読む)

論理回路および半導体装置

【課題】微細化に適し、且つ演算処理を行う各種論理回路において、演算処理を実行中に電源をオフする場合でも、電源をオフする直前に入力された電位を保持できる論理回路を提供することである。また、該論理回路を有する半導体装置を提供することである。

【解決手段】入力端子および出力端子と、入力端子および出力端子に電気的に接続された主要論理回路部と、入力端子および主要論理回路部に電気的に接続されたスイッチング素子を有し、スイッチング素子の第1端子は入力端子と電気的に接続されており、スイッチング素子の第2端子は主要論理回路を構成する1以上のトランジスタのゲートと電気的に接続されており、スイッチング素子は、オフ状態におけるリーク電流がチャネル幅1μmあたり1×10−17A以下のトランジスタとする論理回路である。また、このような論理回路を有する半導体装置である。

(もっと読む)

電圧レギュレータ

【課題】ノーマリオン型のトランジスタをオンオフ駆動できるようにする。

【解決手段】電圧レギュレータは,入力電圧に接続されたノーマリオン型の第1のトランジスタと,第1のトランジスタと出力端子との間に設けられたインダクタと,第1のトランジスタとインダクタとの接続ノードとグランド電圧との間に設けられた還流回路と,第1のトランジスタのゲートに駆動信号を供給する駆動回路と,グランド電圧に接続され,第1のトランジスタのオンオフ動作により接続ノードに生成されるパルス信号に基づいて負電圧を生成し,負電圧を駆動回路に供給する負電圧生成回路とを有する。

(もっと読む)

ゲートタイミング制御回路

【課題】半導体スイッチ,負荷電流,温度,主回路構成等によるサージ電圧の波形に応じて半導体スイッチの動作タイミングを調整することなく、各半導体スイッチの電圧分担を均等化させる。

【解決手段】直列接続された複数の半導体スイッチA,Bに出力されるゲート信号のタイミングを調整するゲートタイミング制御回路3において、コンパレータ4,4により、各半導体スイッチA,BのVce検出(A),(B)と、予め設定されたしきい値とを比較してVce検出における立ち上がりのタイミングを示すVce信号(A),(B)を出力する。そして、時間差制御部8において、ゲート信号に基づいて、前記各Vce信号(A),(B)の変化のタイミングが整合するように生成されたゲート出力(A),(B)をゲートドライバ2に出力する。

(もっと読む)

半導体装置

【課題】インバータ回路とそれを構成するスイッチ素子を駆動・制御する駆動・制御回路において、追加回路規模が少なく、所望の負電位を動的に印加できる駆動・制御回路、また、インバータ回路における短絡電流を削減し、損失の少ない電力変換回路を提供する。

【解決手段】半導体装置において、第1,第2スイッチ素子(下側アームのスイッチ素子LSW,同様の上側アームのスイッチ素子)を有するインバータ回路と駆動回路(L側ゲート駆動回路LGD,同様のH側ゲート駆動回路)と制御回路とを有し、駆動回路は、スイッチ素子のゲート電極をソース電位に駆動する回路と、スイッチ素子のゲート電極を負電位に駆動する回路とを有し、負電位に駆動する回路の出力ノードとスイッチ素子との間に直列にコンデンサが接続され、制御回路は、スイッチ素子がオフ状態からオン状態になる直前のスイッチ素子のゲート電極の電圧をソース電位と同じであるように制御する。

(もっと読む)

半導体デバイス駆動回路及び半導体装置

【課題】電源電圧が変動しても半導体デバイスのオン動作及びオフ動作を安定して駆動できる半導体デバイス駆動回路を得る。

【解決手段】ドライブ回路10は、入力回路11より得られる制御信号S11に基づき、インバータG4から電源電圧VCCにより決定される“H”(オンレベル)、あるいは接地電圧GNDにより決定される“L”(オフレベル)の出力電圧VOUT1を駆動信号として半導体デバイスQ1のゲートに出力する。基準電源部14は抵抗R1及びR2の直列接続により、電源電圧VCC,接地電圧GND間の電位差を所定の分圧比率(抵抗R1及びR2による抵抗比)で分圧して得られる電圧が基準電圧VREF1として得られる。バッファ回路8は基準電圧VREF1により決定される基準信号となる出力電圧VOUT2を半導体デバイスQ1のソースに付与する。

(もっと読む)

半導体集積回路

【課題】絶縁ゲート型半導体素子を駆動する半導体集積回路内において、貫通電流の発生を抑制することが可能な技術を提供することを目的とする。

【解決手段】半導体集積回路は、制御信号Vinを遅延させて得られる遅延信号を、PMOS1及びNMOS2のゲート端子に出力する遅延回路19を備える。NMOS4が、第2出力信号の変化に応じてオンからオフに切り替えられるタイミング(t2)は、PMOS1が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t2)よりも遅くなく、かつ、PMOS3が、第1出力信号の変化に応じてオンからオフに切り替えられるタイミング(t7)は、NMOS2が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t7)よりも遅くない。

(もっと読む)

差動入力バッファ

【課題】動作モード切り換え時におけるノイズを抑制する。

【解決手段】差動入力バッファ1は、動作モードを通常状態又は省電力状態のいずれかに切り換える電源回路MN1,MN2と、ソースフォロア回路を構成する半導体素子MP1,MP3及びMP2,MP4のそれぞれの寄生容量の合計である第1の寄生容量に対応する第2の寄生容量を有する半導体素子MP7,MP8により構成されるダミー回路とを有し、動作モードの切り換え時に第1の寄生容量に起因して発生する電流の流通方向と、動作モードの切り換え時に第2の寄生容量に起因して発生する電流の流通方向とが共通の配線において相反する構成を有する。

(もっと読む)

絶縁ゲート型スイッチング素子のゲートの電位を制御する半導体装置、及び、回路

【課題】 絶縁ゲート型スイッチング素子のゲートの電位を制御する半導体装置であって、低速スイッチング用と高速スイッチング用とで共通して使用可能な半導体装置を提供する。

【解決手段】 絶縁ゲート型スイッチング素子のゲートの電位を制御する信号を出力する半導体装置であって、第1信号出力端子を有しており、第1電位と第1電位よりも高い第2電位の間で変動する基準信号の入力を受けるか、または、内部で前記基準信号を生成することが可能であり、前記基準信号が第1電位にあるときには第3電位となり、前記基準信号が第2電位にあるときには第3電位よりも高い第4電位となる信号を第1信号出力端子に出力する第1動作と、前記基準信号が第1電位にあるときには第4電位となり、前記基準信号が第2電位にあるときには第3電位となる信号を第1信号出力端子に出力する第2動作とを切り換えて実行することができる。

(もっと読む)

81 - 90 / 1,196

[ Back to top ]