国際特許分類[H03K17/687]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 特定の構成要素の使用によって特徴づけられたもの (2,578) | 能動素子として半導体装置を用いるもの (2,114) | 装置が電界効果トランジスタであるもの (1,712)

国際特許分類[H03K17/687]の下位に属する分類

制御回路と出力回路の間が電気的に絶縁されたもの

いくつかの入力または出力端子をもつスイッチング装置,例.マルチプレクサ,分配器 (320)

誘導性負荷をもつもの (196)

国際特許分類[H03K17/687]に分類される特許

51 - 60 / 1,196

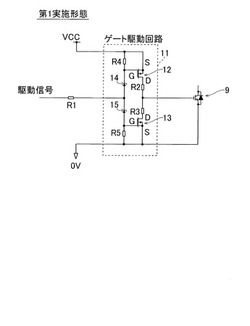

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

半導体装置

【課題】フォトカプラの一次側に流れる電流を制限するため抵抗を回路基板上に実装することなく、フォトカプラの一次側に流れる電流を制限できるようにする。

【解決手段】制御IC11a〜11cには、フォトカプラ21a〜21cの一次側に流れる電流を制限する抵抗17a〜17cをそれぞれ内蔵し、トランジスタ16a〜16cがそれぞれ導通した時に流れる電流を抵抗17a〜17cをそれぞれ介して発光素子22a〜22cに導くことにより、フォトカプラ21a〜21cの一次側に流れる電流を制限する。

(もっと読む)

トランジスタ回路、双方向スイッチ回路、ダイオード回路及びトランジスタ回路の製造方法

【課題】トランジスタのゲートへの電流を防ぐ。

【解決手段】ノーマリーオン型の第1トランジスタと、ドレインが、第1トランジスタのソースと接続され、第1トランジスタとカスコード接続されたノーマリーオフ型の第2トランジスタと、第2トランジスタのソースと第1トランジスタのゲートとの間に設けられた、第2トランジスタのソースから第1トランジスタのゲートへと流れる電流を抑制する第1電流抑制部とを備えるトランジスタ回路を提供する。

(もっと読む)

2線式交流スイッチ

【課題】2線式交流スイッチの低消費電力化を実現する。

【解決手段】

交流電源と負荷とを結ぶ電路に挿入される2線式交流スイッチであって、スイッチ端子S1、S2と、スイッチ端子間のオンオフを制御するためのゲート端子G1、G2と、基板端子Subとを有し、スイッチ端子間に双方向に電流を流すことができ、スイッチ端子S1が交流電源1に接続され、スイッチ端子S2が負荷2に接続される半導体スイッチからなるメインスイッチ3と、メインスイッチの基板端子Subを接地するかフローティングにするかを切り替えるサブスイッチ9と、を備える。

(もっと読む)

低Vf逆導通FET回路及び多機能FET回路用IC

【課題】内部ダイオード又は外部ダイオードを使用せずに、逆方向へ導通可能なMOS−FET回路を提供すること。

【解決手段】MOS−FET(10)と、このMOS−FET(10)のドレインをマイナス入力に接続し、ソースをプラス入力に接続したオペアンプ(15)と、このオペアンプ(15)の出力を一方の入力とし、ゲート端子(14)を他方の入力とした第一OR回路(17)とからなり、前記第一OR回路(17)の出力を前記MOS−FET(10)のゲートに接続した。

(もっと読む)

PLL

【課題】 安定性と即応性を備えたPLLを提供すること。

【解決手段】 本発明の実施形態によるPLLは、位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御する。

(もっと読む)

スイッチモジュールおよびそれを用いた試験装置

【課題】半導体スイッチの低周波数領域での歪み特性を改善する。

【解決手段】制御ポートP3には、制御電圧VCが入力される。伝送路10は、入力ポートP1と出力ポートP2の間を接続する。シャントスイッチ20は、伝送路10と接地端子の間に設けられる。シャントスイッチ20は、そのドレイン、ソースの一方が伝送路10と接続され、そのドレイン、ソースの他方が接地端子に接続されるFET22を備える。第1抵抗R1は、FET22のゲートと制御ポートP3の間に設けられる。第2抵抗R2は、FET22のゲートと伝送路10の間に設けられる。

(もっと読む)

ゲートドライブ回路

【課題】ターンオン時のスイッチング特性が変動せず、電力損失を発生せずにスイッチング素子を安定してターンオンさせることができるゲートドライブ回路。

【解決手段】ワイドバンドギャップ半導体かなるスイッチング素子Q1のゲートに制御回路からの制御信号を印加することによりスイッチング素子をオンオフ駆動させるゲートドライブ回路であって、制御回路とスイッチング素子のゲートとの間に接続されたコンデンサC1と抵抗R1とからなる並列回路と、並列回路にコンデンサC2とスイッチング素子Q2と抵抗R2からなる直列回路がさらに並列接続され、コンデンサC2とスイッチング素子Q2との接続点にダイオードD1のアノードが接続され、ダイオードD1のカソードとスイッチング素子Q2のゲートはスイッチング素子Q1のソースに接続され、制御信号のオフ信号に対してスイッチング素子Q1ゲートを負電位にバイアスする。

(もっと読む)

電流制御用半導体素子およびそれを用いた制御装置

【課題】ゲインa、およびオフセットbの変動を動的に補正することで、1チップのIC内で高精度な電流検出が可能な電流制御用半導体素子、およびそれを用いた制御装置を提供することにある。

【解決手段】

同一半導体チップ上に、トランジスタ4と、電流−電圧変換回路22とADコンバータ23とを有する。参照電流生成回路6,6’は、負荷2の電流に電流パルスIcを重畳して、ADコンバータが出力する電圧デジタル値を変動させる。ゲインオフセット補正部8は、参照電流生成回路6,6’による電圧デジタル値の変動を信号処理して、ADコンバータ23が出力する電圧デジタル値と負荷の電流デジタル値の線形関係式におけるゲインa,a’及びオフセットb,b’を動的に取得する。電流デジタル値演算部12は、ゲインオフセット補正部8により取得されたゲイン及びオフセットを用いて、ADコンバータが出力する電圧値を補正する。

(もっと読む)

アナログスイッチ回路およびマルチプレクサ回路

【課題】 外部端子の雑音の影響を抑制しつつ、リーク電流を低減する。

【解決手段】 アナログスイッチ回路は、第1ノードと第2ノードとの間に配置された第1スイッチと、第2ノードと第3ノードとの間に配置された第2スイッチと、所定の電圧が供給される第4ノードと第2ノードとの間に配置された第3スイッチと、少なくとも2種類の制御信号を受け、第1スイッチおよび第2スイッチをオンし、かつ、第3スイッチをオフする第1制御と、第1スイッチ、第2スイッチおよび第3スイッチをオフする第2制御と、第1スイッチおよび第2スイッチをオフし、かつ、第3スイッチをオンする第3制御とのいずれかを、制御信号の組み合わせに基づいて実施する制御部とを有している。

(もっと読む)

51 - 60 / 1,196

[ Back to top ]