国際特許分類[H03K17/687]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 特定の構成要素の使用によって特徴づけられたもの (2,578) | 能動素子として半導体装置を用いるもの (2,114) | 装置が電界効果トランジスタであるもの (1,712)

国際特許分類[H03K17/687]の下位に属する分類

制御回路と出力回路の間が電気的に絶縁されたもの

いくつかの入力または出力端子をもつスイッチング装置,例.マルチプレクサ,分配器 (320)

誘導性負荷をもつもの (196)

国際特許分類[H03K17/687]に分類される特許

11 - 20 / 1,196

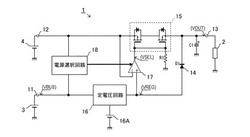

電源切換装置

【課題】電圧変動の少ない電源切り換えを確実に行うことができる電源切換装置を提供する。

【解決手段】第2電源が接続される第2電源接続部、第2電源の電圧よりも高い電圧の第1電源が接続される第1電源接続部、負荷回路が接続される電源出力部、定電圧回路の出力端子と電源出力部とを接続するダイオード、第1電源接続部とダイオードとの間に挿入され第1電源の電圧を第2電源の電圧よりもダイオードの順方向電圧降下分高い電圧まで降圧する定電圧回路、第2電源接続部と電源出力部との接続をオン/オフするMOSスイッチと、第1電源接続部から電源が供給され、第2電源接続部または電源出力部の電圧と定電圧回路の出力電圧とを比較し、定電圧回路の出力電圧が第2電源接続部または電源出力部の電圧よりも高いとき、第1電源の電圧をMOSスイッチに導通することによってMOSスイッチをオフする比較回路と、を備える。

(もっと読む)

制御装置

【課題】電源ユニットの出力ラインにおける地絡などの故障に対し、電源の保護及び故障の検知を行う。

【解決手段】サブ電源供給ラインLSに、サブ電源101側をソースとして第1MOSFET102を直列に接続し、第1MOSFET102のドレインにドレインを接続させて第2MOSFET103を直列に接続する。制御ユニット200内のサブ電源供給ラインLSにも、サブ電源101側をソースとして第3MOSFET202を直列に接続し、第3MOSFET202のドレインにドレインを接続させて第4MOSFET203を直列に接続し、第1〜第4MOSFETを制御することで、サブ電源101の電力を負荷201に対して供給する。各MOSFETのドレイン電圧、及び、第2MOSFET103と第3MOSFET202との間の電圧をモニタし、MOSFETの故障及びサブ電源供給ラインLSの故障を診断する。

(もっと読む)

スタック電圧耐性を高めるためのキャパシタンス調整

【課題】 印加されるRF電圧Vswに制御可能に耐えるRFスイッチ、又はこのようなスイッチの製造方法を提供する。

【解決手段】 スイッチは直列接続された構成FETのストリングを有し、このストリングのノードは隣接するFETの各対の間にある。方法は、各構成FETにわたって分布するRFスイッチ電圧の不一致を減らすよう、容量的にストリングを有効に調整すべくストリングの異なるノードの間のキャパシタンスを制御し、それによって、スイッチ・ブレイクダウン電圧を高める。キャパシタンスは、例えば、ストリングのノードの間に容量特性配置することによって、及び/又は異なる構成FETの設計パラメータを変化させることによって、制御される。各ノードについて、ノードに現れるVswの比率による各有意なキャパシタの積の和は、おおよそ零になるよう制御され得る。

(もっと読む)

誘導性負荷駆動装置

【課題】電流回生ルートから電流還流ルートへの切替時におけるホールドコンデンサの電荷抜けを抑制して電流検出精度の向上を実現可能な誘導性負荷駆動装置を提供する。

【解決手段】第1のスイッチング素子と、第2のスイッチング素子と、還流回路と、逆起電流回生回路と、第2のスイッチング素子とアースとの間に介挿されたシャント抵抗とを備えた誘導性負荷駆動回路から誘導性負荷に供給される駆動電流を検出する誘導性負荷駆動装置であって、シャント抵抗の両端に接続された差動増幅器と、第1及び第2のスイッチング素子を制御するプロセッサと差動増幅器の出力端子とを結ぶ配線に介挿されたサンプルスイッチと、プロセッサから第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから所定の遅延時間の経過後にサンプルスイッチをオンにさせる遅延回路とを備える。

(もっと読む)

電圧スイッチ回路

【課題】低濃度ドープのPMOSトランジスタを用いて、高電圧ストレスに耐える電圧スイッチ回路を提供する。

【解決手段】該電圧スイッチ回路は、出力回路210、第1の電圧降下制御回路220、第2の電圧降下制御回路230、第3の電圧降下制御回路240、および入力回路250を備えている。また、高電圧源HVの電圧振幅は、基準電圧源Vrefの電圧振幅よりも高く、基準電圧源Vrefの電圧振幅は、論理電圧源VDDの電圧振幅よりも高い。

(もっと読む)

電界効果トランジスタのゲート電位制御回路

【課題】FETのゲートドライブ回路に正負の電源を必要とせず、簡単な受動素子のみの回路で、ゲート電位に正極/負極電位を印加しFETの高速スイッチングドライブを可能とする。

【解決手段】電流路が導通する電位を超える電位1を、電流路の一端を基準電位として、制御端に容量素子を介して断続的に印加されるべく構成され、電位1が印加されたとき、電位1が前記定電圧素子1に対して、電流路が導通に要す定電圧素子1の有する降伏電圧1を発生すべく、かつ電位1が定電圧素子2に対して順方向に、電位1が印加された後、電位1が低下されたとき、電位1により容量素子に充電された電位2が電流路の一端を基準電位とし定電圧素子2に対して、電位1と逆極性の、定電圧素子2の有する降伏電圧2を発生すべく、かつ電位2が定電圧素子1に対して順方向に、定電圧素子1と定電圧素子2の直列接続回路を、制御端と電流路の一端との間に介在させた。

(もっと読む)

出力ドライバー回路

【課題】nMOSトランジスタM2のゲート−ソース間に加わる電圧を耐圧電圧未満に制限する際に消費電流の増加を抑制する。

【解決手段】pMOSトランジスタM1がオフし、かつnMOSトランジスタM2がオンしたとき、ツェナーダイオードZD2により、nMOSトランジスタM2のゲート端子とソース端子との間の電圧を一定電圧に制限する。nMOSトランジスタM2のゲート端子とソース端子との間に耐圧電圧よりも高い電圧が加わることを避けることが可能になる。このとき、定電流電源20bが電源からツェナーダイオードZD2を通してグランドに流れる電流を制限する。電源からトランジスタM3、M5b、M6bを通してnMOSトランジスタM2のゲート端子に流れる電流をnMOSトランジスタM6bが制限する。

(もっと読む)

RFパルス信号生成用スイッチング回路、RFパルス信号生成回路、および物標探知装置

【課題】安定動作させながら、RFパルス信号の波形を高速に立ち下げることができるRFパルス信号生成用スイッチング回路を提供することにある。

【解決手段】ドレインスイッチング回路21は、n型からなる第1、第2、第3のFET211,212,213を備える。第1、第3のFET211,213のゲートには、制御パルスが印加され、ソースは接地されている。第1のFET211のドレインは、第2のFET212のゲートに接続し、第2のFET212のドレインには、駆動電圧Vdsが印加される。第2のFET212のソースと第3のFET213のドレインは接続され、接続点がパワーFET31のドレインに接続されている。第2のFET212のゲートソース間には、第2のFET212がオフ状態からオン状態へ遷移する際のゲート電圧を補償するための電荷を供給するコンデンサ215が接続されている。

(もっと読む)

負荷制御装置

【課題】高デューティ領域においてデューティ比が不正確になるのを防止することにより、デューティ比の精度を向上させた負荷制御装置を提供する。

【解決手段】三角波生成回路5が、負荷2に供給される電源電圧VIから三角波VC1を生成する。パルス駆動回路6が、三角波生成回路5により生成される三角波VC1と基準電圧Vkとの比較に応じたデューティ比の駆動パルスを負荷2に供給する。基準電圧生成回路7が、電源電圧VIが増加するに従って基準電圧Vkを増加または減少させて駆動パルスのデューティ比を減少させる。周波数調整回路8が、電源電圧VIが所定電圧以下のときに、三角波生成回路5により生成される三角波VC1の周波数を低くして駆動パルスの周波数を低くする。

(もっと読む)

半導体装置及びアナログスイッチの制御方法

【課題】高い電圧を有する入力信号に対して適切に動作するアナログスイッチを有する半導体装置を提供する。

【解決手段】入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチと,入力端子に印加される入力電圧に応じて,Pチャネルトランジスタの第1ゲート電圧及び第1バックゲート電圧と,Nチャネルトランジスタの第2ゲート電圧及び第2バックゲート電圧とのそれぞれの電位を可変生成する可変電圧回路と,アナログスイッチを導通または非導通に制御する制御信号を可変電圧回路に供給する制御回路とを有する。可変電圧回路は,導通に制御する制御信号に応答して,可変生成される第1ゲート電圧と第2ゲート電圧とをPチャネルトランジスタとNチャネルトランジスタのゲートにそれぞれ出力する。

(もっと読む)

11 - 20 / 1,196

[ Back to top ]