国際特許分類[H03K19/00]の内容

国際特許分類[H03K19/00]の下位に属する分類

信頼性を増すための変形 (215)

フェイルセーフ回路 (8)

スイッチ動作の高速化のための変形 (58)

結合装置;インターフェイス装置 (1,927)

特定の構成要素を用いるもの (1,730)

論理機能によって特徴づけられたもの,例.アンド,オア,ノア,ノット回路 (214)

国際特許分類[H03K19/00]に分類される特許

81 - 90 / 669

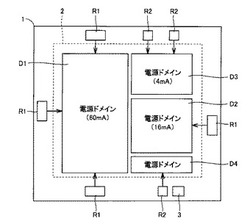

半導体チップおよびその設計方法

【課題】設計期間が短く、面積効率が高く、電源配線における電圧降下が小さな半導体チップと、その設計方法を提供する。

【解決手段】この半導体チップは、複数の電源ドメインD1〜D4に分割された内部回路2を備える。互いに異なる電流駆動能力を有する複数種類のレギュレータR1,R2を予め準備しておき、各電源領域毎に、当該電源領域の最大負荷電流を供給するために必要なレギュレータの種類と数を選択し、選択した1または2以上のレギュレータによって当該電源領域用の電源回路を構成する。したがって、設計期間が短くて済む。

(もっと読む)

集積回路装置及び電子機器

【課題】センサーデバイスからの検出信号の精度の高いA/D変換を実現できる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、電源電圧VDDAを生成する電源回路60と、電源回路60から電源電圧VDDAが供給され、供給された電源電圧VDDAに基づいて動作し、電源電圧VDDAにより規定されるA/D変換範囲で、センサーデバイス30からの検出信号に対応する信号についてのA/D変換を行うA/D変換器ADCと、電源回路60から電源電圧VDDAが供給され、供給された電源電圧VDDAをセンサーデバイス30に供給する電源端子PVDAを含む。

(もっと読む)

リーク電流低減回路

【課題】 間欠動作する論理回路の動作停止時(待機時)のリーク電流を低減するとともに、さらに論理回路の動作時の駆動電流を十分に供給可能とする。

【解決手段】 論理回路と電源の間に接続のパワースイッチを論理回路の間欠動作に合わせて制御する構成において、2つのパワースイッチは論理回路と正の電源電位との間にnMOSトランジスタを接続し、論理回路と接地電位との間にpMOSトランジスタを接続した構成とし、論理回路の動作停止時にpMOSトランジスタのゲート端子を正の電源電位に接続して非導通とし、論理回路の動作時にpMOSトランジスタのゲート電位を接地電位に接続して導通させるスイッチを備え、論理回路の動作停止時にnMOSトランジスタのゲート端子を接地電位に設定して非導通とし、論理回路の動作時にnMOSトランジスタのゲート端子を正の電源電位以上の電位に設定して導通させる電圧変換器を備える。

(もっと読む)

半導体装置およびその制御方法

【課題】半導体装置のデータ入力回路における消費電力を削減すること。

【解決手段】半導体装置は、クロック信号の立ち上がりエッジおよび立ち下がりエッジの少なくともいずれか一方の近傍の期間において活性状態となる制御信号を生成して出力する制御信号生成回路と、制御信号が活性状態である期間においてデータ信号を受信可能な活性状態となり、それ以外の期間において非活性状態となるデータ入力回路と、を備えている。

(もっと読む)

半導体デバイス回路

【課題】MTCMOS回路を用いた半導体デバイス回路において、アクセススピードを損なわず、スタンバイ電流が少なく、スタンバイ状態からの復帰が早い半導体デバイス回路を提供する。

【解決手段】第1のPMOSFETと第1のNMOSFETとを含む機能回路を備えた半導体デバイス回路において、アクティブモード時に第1のPMOSFETを電源電圧源に接続し、スタンバイモード時に電源電圧源に接続しないように制御する第2のPMOSFETと、アクティブモード時に第1のNMOSFETを接地側電圧源に接続し、スタンバイモード時に接地側電圧源に接続しないように制御する第2のNMOSFETと、電源電圧源に接続されかつ第1のPMOSFETに並列に接続されその出力信号を保持する第3のPMOSFETと、接地側電圧源に接続されかつ第1のNMOSFETに並列に接続されその出力信号を保持する第3のNMOSFETとを備えた。

(もっと読む)

半導体装置及び半導体装置の電源制御方法

【課題】スタンバイ状態への設定と解除が頻繁に繰り返されることにより、消費電力が増大することを避けることのできる半導体装置を提供する。

【解決手段】内部回路50と、第1制御信号を受けて内部回路への電源供給を制御する電源制御回路40と、第2制御信号を受けて第1制御信号を出力する制御信号発生回路30と、を備え、制御信号発生回路30は、第2制御信号の非活性期間が第1の期間未満であるときに第1制御信号を非活性状態とせず、第1の期間以上であるときに第1制御信号を非活性状態とする。

(もっと読む)

半導体装置及びその制御方法

【課題】半導体装置に電源遮断(パワーゲーティング)を適用する際に、待機モード時の出力が一意に定まらない場合がある。そのような場合には、複数のバッファ電源線と複数の電源セレクタを用意することでパワーゲーティングを適用する。しかし、このような方法では回路面積が増加してしまうという問題がある。

【解決手段】そこで、パワーゲーティングを適用した回路が非活性状態から活性状態に復帰する際のタイミングを半導体装置に発行されたコマンド、又はサブ電源線が復帰電圧の監視、に基づいて定めることとする。

(もっと読む)

半導体集積回路

【課題】電源遮断時に、電源遮断対象ブロックへの電源配線を有効に活用することのできる半導体集積回路を提供する。

【解決手段】実施形態の半導体集積回路は、第1の電源パッドと、第2の電源パッドと、第1の電源パッドに接続された第1の電源配線と、第2の電源パッドに接続された第2の電源配線と、を備え、第1のスイッチを介して第1の電源配線に接続される電源遮断対象ブロックと、第2の電源配線に接続される常時電源供給対象ブロックと、第1の電源配線と第2の電源配線との間に接続された第2のスイッチと、を備える。

(もっと読む)

テスト回路及び半導体集積回路

【課題】入力されたパルス波形の遅延及び鈍りの影響を抑制し、より高精度なテストを実現すること。

【解決手段】テスト回路6は、複数の論理値を保持する複数のデータ保持/選択回路と、複数の外部端子に含まれる互いに異なる外部端子を介して入力される論理値間の伝播遅延量の検出に基づいて、複数のデータ保持/選択回路それぞれに対して、複数のデータ保持/選択回路それぞれが保持している複数の論理値のいずれを出力すべきかを個別に制御するスキュー調整回路20と、基準クロックの立上がり及び立下りそれぞれに応じて外部端子に入力した論理値を第1及び第2論理値として個別に検出すると共に、個別に検出した第1及び第2論理値の少なくとも一方と期待値間の比較に基づいて、第1及び第2論理値の一方をデータ保持/選択回路に供給する複数の論理値生成/選択回路と、を備える。

(もっと読む)

半導体集積回路

【課題】他の回路のタイミングに影響を与えずに、動作モードにおける組み合わせ回路のオフリーク電流を低減させる半導体集積回路を提供する。

【解決手段】組み合わせ回路32と、組み合わせ回路の出力信号をクロック信号CKに同期して保持する順序回路100と、を備え、順序回路は、クロック信号のエッジを検出してパルスを生成するパルス生成回路と、出力信号をパルスに同期してラッチするラッチ回路と、クロック信号とパルスとから組み合わせ回路の電源制御信号を生成する電源制御信号生成回路と、電源制御信号により導通非導通が制御され、導通するときに組み合わせ回路に電源を供給する電源スイッチと、を備える。

(もっと読む)

81 - 90 / 669

[ Back to top ]