国際特許分類[H03K19/00]の内容

国際特許分類[H03K19/00]の下位に属する分類

信頼性を増すための変形 (215)

フェイルセーフ回路 (8)

スイッチ動作の高速化のための変形 (58)

結合装置;インターフェイス装置 (1,927)

特定の構成要素を用いるもの (1,730)

論理機能によって特徴づけられたもの,例.アンド,オア,ノア,ノット回路 (214)

国際特許分類[H03K19/00]に分類される特許

51 - 60 / 669

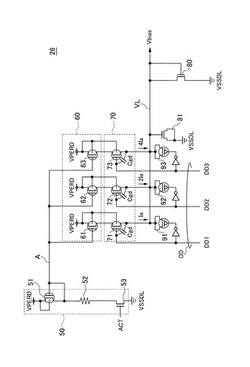

半導体装置

【課題】切り替えスイッチのオンオフに伴うノイズがバイアスラインに重畳するのを防ぐ。

【解決手段】バイアス電流が流れるバイアスラインVLと、バイアス電流の量を制御信号DDに基づいて切り替える切り替えスイッチ70と、制御信号DDが供給される制御ラインとバイアスラインVLとの間の寄生容量を介して制御信号DDの変化時に生じるバイアスラインVLの電位変動を相殺する相殺回路91〜93とを備える。本発明によれば、切り替えスイッチ70のオンオフに伴ってバイアスラインVLに生じるノイズを相殺することが可能となる。

(もっと読む)

電子回路

【課題】発振回路部の信号反転素子及びインターフェース回路部のインターフェース回路部のインターフェース集積回路素子で消費される電流を抑えて消費電力が少ない電子回路を提供する。

【解決手段】発振回路部とインターフェース回路部と被駆動回路部と備えた電子回路であって、発振回路部用電源電圧印加端子と発振回路部の間に発振回路部用電流制限抵抗が設けられ、インターフェース回路部用電源電圧印加端子とインターフェース回路部との間にインターフェース回路部用電流制限抵抗が設けられ、発振回路部用電流制限抵抗の両端部からグランドに接続されている第一のコンデンサが設けられ、インターフェース回路部用電流制限抵抗の両端部からグランドに接続されている第二のコンデンサが設けられ、インターフェース回路部から出力され被駆動回路部に入力される信号電圧が被駆動回路部が動作するために必要な電圧より大きいことを特徴とする。

(もっと読む)

演算およびスリープ・モード中のデータ格納回路並びに方法

【課題】スリープ・モード中に信号を格納するための回路を提供する。

【解決手段】スリープ信号を受け取るスリープ信号入力と、クロック信号を受け取るクロック信号入力と、クロック信号でクロックされる複数のラッチと、クロック信号でクロックされるトライステート素子であって、トライステート素子は1つの入力に、少なくとも1つの格納ラッチが接続され、格納ラッチは複数のラッチの1つであり、トライステート素子は格納ラッチの入力を、予め定められたクロック信号値に応答して選択的に分離するトライステート素子とを含み、回路への電源供給が、スリープ信号に応答して、回路の少なくとも1部の電圧差が低減されて回路の部分の電源が遮断され、格納ラッチに掛かる電圧差が維持され、トライステート素子で受け取られるクロック信号が予め定められた値に保持されて、格納ラッチの入力が分離される。

(もっと読む)

内部電源電圧生成回路

【課題】ロジック回路の動作時の貫通電流が、ロジック回路を構成するP型トランジスタとN型トランジスタの閾値電圧ばらつきの影響により過大とならず、消費電流を抑えることが可能な、内部電源電圧生成回路の提供。

【解決手段】内部電源端子の内部電源電圧を生成し、前記内部電源電圧をロジック回路に供給する内部電源電圧生成回路であって、ゲートに与えられる電圧をソースフォロワ出力するトランジスタを有し、内部電源電圧の値が、N型トランジスタの閾値電圧と、P型トランジスタの閾値電圧の絶対値の和に基づいて与えられ、前記N型トランジスタは、前記ロジック回路内部のN型トランジスタと同一の製造プロセスで形成され、前記P型トランジスタは、前記ロジック回路内部のP型トランジスタと同一の製造プロセスで形成される、内部電源電圧生成回路、とした。

(もっと読む)

レベルシフト回路

【課題】消費電流の増加を抑制しつつ電源投入時にレベルシフタの状態を確定させる技術を提供する。

【解決手段】信号レベル変換部(11)と、安定化回路(12)とを具備するレベルシフト回路を構成する。安定化回路(12)は、第2電源電圧供給ノード(ND1)と接続ノード(ND2)との接続を制御する第1スイッチ(P3)と、接続ノード(ND2)電圧に応答して接地電圧供給ノード(GND)と出力ノード(ND3)との接続を制御する第2スイッチ(N3)とを備えることが好ましい。そして、第1スイッチ(P3)は、第2電源電圧(VDD)が、第1中間電圧を超えないときに、第2電源電圧供給ノード(ND1)と接続ノード(ND2)とを接続する。また、第2スイッチ(N3)は、第2電源電圧供給ノード(ND1)の電圧に応答して、出力ノード(ND3)と接地電圧供給ノード(GND)とを接続する。

(もっと読む)

低リーク電圧検出回路

【課題】ゲート電極駆動電圧信号が不十分な電圧のためにリーク電流が発生することのない低リーク電圧検出回路及び方法を提供する。

【解決手段】伝送ゲート202、フィードバック通路204、制御器200を備え、第1の電位によって給電された第1の装置と第2の電位によって給電された第2の装置との間に置かれた低リーク電圧検出回路である。第1の装置と第2の装置との間における電位のミスマッチは、リーク電流が第2の装置の入力段を流れることを招く可能性がある。低リーク電圧検出回路を採用することによって、第1の装置の発生した高論理レベルは、対応的にほぼ第2の電位の振幅と等しい高論理レベルに転換される。

(もっと読む)

内部電源電圧生成回路

【課題】ロジック回路の動作時、貫通電流が、製造ばらつきの影響により過大とならず、消費電流を抑えることが可能な、内部電源電圧生成回路の提供。

【解決手段】内部電源端子の内部電源電圧を生成し、前記内部電源電圧をロジック回路に供給する内部電源電圧生成回路であって、ゲートに与えられる電圧をソースフォロワ出力するトランジスタと、前記ゲートに与えられる電圧をソースフォロワ出力するトランジスタの最大電流を制限する電流制限回路と、を備え、ロジック回路への最大電流、及び消費電流を抑えることが可能な構成とした。

(もっと読む)

定電圧回路とその半導体装置

【課題】 ツェナーダイオードと同等の動作を行える回路ないしは半導体装置を提供することを目的とする。

【解決手段】 実施形態の基準電圧発生回路は、第1のFETと、第2のFETと、一方を電源に接続し他方を前記第1のFETのドレインに接続した第1の抵抗と、前記第1のFETのドレイン−ゲート間に接続した第2の抵抗とを有し、前記第2のFETのゲート−ソース間を接続し、前記第2のFETのドレインを前記第1のFETのゲートに接続し、前記第1のFETのドレインが基準電圧を出力し、前記第1のFETのソースと前記第1のFETのソースがグランド又は他の回路と接続していることを特徴とする。

(もっと読む)

電圧識別装置及び時計制御装置

【課題】回路規模及び消費電流の増大を抑制しながら識別対象電圧の大きさを精度良く識別することができる電圧識別装置及び時計用制御装置を提供する。

【解決手段】基準電圧生成回路12と、被印加線18並びに電圧線VSH及び接地線GNDが導通可能となるように電圧線VSHと接地線GNDとの間に挿入されると共に、被印加線18に印加された識別対象電圧の大きさに応じてスイッチングを行うスイッチング回路20を備え、被印加線18に印加された識別対象電圧の大きさと閾値とを比較することにより識別対象電圧の大きさを識別する識別回路14と、識別回路14に対して識別対象電圧の大きさを識別させる間、電圧線VSHと接地線GNDとの間に流れる電流の大きさが所定の大きさに保たれるようにスイッチング回路20と接地線GNDとの間の抵抗22を制御可能とする制御部16と、を含む。

(もっと読む)

通信モジュール、リーダライタ

【課題】部品を内蔵できる配線板を有する通信モジュールであって、アンテナの特性に応じて整合の調整が可能な通信モジュールおよびこれを用いたリーダライタを提供すること。

【解決手段】配線板と、配線板に備えられた通信処理用ICと、通信処理用ICに電気的に接続されて配線板に備えられた、外部に設けられるアンテナとの整合をとる整合回路と、を具備し、整合回路が、キャパシタまたはインダクタを少なくとも含む受動素子回路網の回路であり、該受動素子回路網を構成する回路エレメントのうちの少なくともひとつが、配線板に内蔵された第1の受動素子部品と、配線板の面上に実装された、該第1の受動素子部品と同じ種の受動素子部品である第2の受動素子部品との並列接続または直列接続でできた回路エレメントである。

(もっと読む)

51 - 60 / 669

[ Back to top ]