国際特許分類[H03K19/00]の内容

国際特許分類[H03K19/00]の下位に属する分類

信頼性を増すための変形 (215)

フェイルセーフ回路 (8)

スイッチ動作の高速化のための変形 (58)

結合装置;インターフェイス装置 (1,927)

特定の構成要素を用いるもの (1,730)

論理機能によって特徴づけられたもの,例.アンド,オア,ノア,ノット回路 (214)

国際特許分類[H03K19/00]に分類される特許

41 - 50 / 669

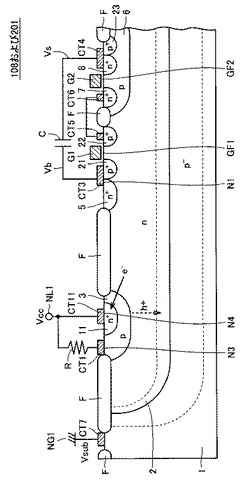

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

半導体装置

【課題】電源制御領域を電源遮断状態から電源供給状態に切り換えた際に生じる突入電流と電源ノイズを低減した半導体装置を提供する。

【解決手段】第1、第2のスイッチセルSWa、SWbと、を有し、第1のスイッチセルSWaは、制御信号CNTに応じてグローバル電源配線GVDDからローカル電源配線LVDDへの電源電圧の供給を開始する第1のスイッチトランジスタ11と、制御信号CNTを伝達する第1の信号伝達部と、を有し、第2のスイッチセルSWbは、制御信号CNTの論理レベルに応じてグローバル電源配線GVDDからローカル電源配線LVDDへの電源電圧の供給を開始する第2のスイッチトランジスタ21と、ローカル電源配線LVDDの電圧値が閾値電圧に達するまでの期間、制御信号CNTの後段回路への伝達を遮断する第2の信号伝達部と、を有する。

(もっと読む)

半導体装置

【課題】ドライバの故障による出力異常を救済することが可能な故障検出救済回路を含んだ半導体装置を提供すること。

【解決手段】故障検知部1は、ドライバ10の出力の期待電位の逆電位となるようにドライバ10の出力にプルアップ抵抗15またはプルダウン抵抗18を接続し、ドライバ10の入力電位と出力電位とを比較することによりドライバ10の故障を検出する。故障救済部2は、故障検知部1によってドライバ10の故障が検出された場合に、期待電位と同電位となるようにドライバ10の出力にプルアップ抵抗26またはプルダウン抵抗29を接続してドライバ10の故障を救済する。したがって、ドライバ10の故障による出力異常を救済することが可能となる。

(もっと読む)

半導体装置

【課題】スタンバイ時のリーク電流と回路面積の増大を抑制する。

【解決手段】第1電源に接続する第1の回路11の入力対に出力が夫々接続された第2及び第3の回路12、13と、前記第1の回路の入力、又は、前記第1の回路の内部ノードに接続された第4の回路14と、を含み、前記第2の回路及び前記第3の回路は、第2電源と第3電源間に接続され、スタンバイ時にパワーゲーティングされる回路を有し、前記第2の回路は、前記第2及び第3電源電位を振幅範囲とする信号を入力し、前記第2の回路の出力は前記第3の回路の入力に接続され、前記第1の回路の出力信号の振幅範囲は、前記第1電源電位と、前記第2又は第3電源電位とされ、前記第4の回路は、パワーゲーティング時に前記第1の回路の前記入力対、又は前記内部ノードの論理値を保持し、スタンバイ時にも前記第1の回路の出力信号の論理を前記入力信号に関連した論理に維持する。

(もっと読む)

半導体集積回路装置

【課題】 集積回路における時間的に変動するばらつきを検出する回路を提供する。

【解決手段】 集積回路内に検出回路100、演算回路101、ばらつき/電圧変換回路113とを設ける。検出回路100において集積回路の特性ばらつきを検出回路100の出力信号の発振周波数として検出する。演算回路101では、タイマ106にて規定した時間間隔毎に検出したばらつき情報をレジスタ111に格納し、統計演算回路112にて統計処理を施し、集積回路の時間的に変動する特性ばらつきを検出する。更に、ばらつき/電圧変換回路113は、検出された特性ばらつきに対応した電圧情報に変換する。

(もっと読む)

レベル生成回路

【課題】 耐圧の低いMOSFETを保護するためにゲート接地として動作する、MOSFETのゲート電圧を生成するための外部電源を不要にする。

【解決手段】 第1電源電圧から一定の大きさの第1電流を生成する定電流生成部と、第1薄膜NMOSFETと第2薄膜NMOSFETから構成され、第1電流に比例した大きさの第2電流を出力する第1カレントミラー回路部と、第2薄膜NMOSFETを保護するためにゲート接地として用いる第3薄膜NMOSFET及び第1厚膜PMOSFETと、第1電源への電流の逆流を防ぐための第1ダイオードと、第3薄膜NMOSFETのゲート−ソース間電圧がマイナスになることを防ぐための第2ダイオードとからなる保護回路部と、第2電流に比例した大きさの第3電流を出力する第2カレントミラー回路部と、第3電流により第1定電圧を生成する第1ツェナーダイオード部とを備える。

(もっと読む)

集積回路装置

【課題】被電源遮断回路の十分な安定化容量を確保しつつ、総回路面積の低減を図る。

【解決手段】高電位電源線VDDと低電位電源線VSSとの間に設けられ、各々が電源遮断スイッチPSW1, PSW2と直列に接続された複数段の被電源遮断回路CC1, CC2を含む集積回路装置であって、奇数段の前記被電源遮断回路CC1と直列に接続された前記電源遮断スイッチPSW1は、第1導電型の第1MOSトランジスタであり、偶数段の前記被電源遮断回路CC2と直列に接続された前記電源遮断スイッチPSW2は、前記第1導電型とは異なる第2導電型の第2MOSトランジスタであり、前記偶数段の前記第2MOSトランジスタPSW2のゲートが、当該偶数段の前段の奇数段における前記第1MOSトランジスタと前記被電源遮断回路の第1電源端子との接続ノードN1に接続される。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

半導体集積回路

【課題】コンデンサの供給する電源電圧の低下により、誤動作を起こす虞がある。

【解決手段】通常動作より低い消費電力状態である低消費電力モードを有する半導体集積回路であって、前記低消費電力モード状態時に、電源電圧レベルを検出する検出手段と、前記検出した電源電圧レベルを記憶する記憶手段と、前記通常動作時よりも小さい電流を流すことで、前記電源電圧を低下させる擬似負荷手段と、前記擬似負荷手段により電流を流す前に前記記憶手段で記憶した第1の電圧レベルに応じて前記検出手段の検出レベルを第2の電圧レベルに切り換える切換え手段と、前記擬似負荷手段により電流を流すことにより低下した前記電源電圧が、前記第2の電圧レベルとなるかを判定し、前記低消費電力モードを解除するか否かの制御を行う制御手段と、を有する半導体集積回路。

(もっと読む)

半導体回路

【課題】ON状態とOFF状態のコントラスト(High/Low比)が高く、消費電力が少なく、端子数および配線数が少ない回路を提供する。

【解決手段】半導体回路は、複数個のNOT回路が縦続接続され、最終段のNOT回路の出力端子と初段のNOT回路の入力端子とが接続されている。NOT回路は、ゲート11とソース13とが一体構造で形成され、ゲート10が入力端子3に接続され、ドレイン12が出力端子5に接続され、ゲート11およびソース13がグランド端子6に接続されたインプレーンダブルゲートトランジスター1と、ゲート20,21およびソース23が一体構造で形成され、ゲート20,21およびソース23がインプレーンダブルゲートトランジスター1のドレイン12に接続され、ドレイン22がバイアス端子4に接続された自己バイアス型インプレーントランジスター2とから構成される。

(もっと読む)

41 - 50 / 669

[ Back to top ]