国際特許分類[H03K19/00]の内容

国際特許分類[H03K19/00]の下位に属する分類

信頼性を増すための変形 (215)

フェイルセーフ回路 (8)

スイッチ動作の高速化のための変形 (58)

結合装置;インターフェイス装置 (1,927)

特定の構成要素を用いるもの (1,730)

論理機能によって特徴づけられたもの,例.アンド,オア,ノア,ノット回路 (214)

国際特許分類[H03K19/00]に分類される特許

71 - 80 / 669

半導体装置

【課題】半導体装置の消費電力を低減しつつ、高速に動作させる。

【解決手段】半導体装置の回路が複数の回路ブロックに分割され、前記回路ブロックがそれぞれ正常に動作し得る最小限度の電圧を供給する複数の電圧供給回路を備え、各前記回路ブロックへの最小限度の電圧を供給する制御内容を記憶する電源電圧制御メモリを有し、前記電源電圧制御メモリの記憶する制御内容に従って前記電圧供給回路が各前記回路ブロックに供給する電圧を切り替える電源切り替え手段を備えた半導体装置を用いる。

(もっと読む)

半導体集積回路

【課題】 内部回路の内部ノードが初期状態に設定されたことを精度よく検出し、内部回路が動作を開始するまでの復帰時間を短縮する。

【解決手段】 第1電源スイッチは、内部電源電圧を受けて動作する内部回路の動作を開始させるための第1電源オン信号の活性化中に、外部電源線を内部電源電圧が供給される内部電源線に接続する。第2電源スイッチは、第2電源オン信号の活性化中に、外部電源線を内部電源線に接続する。検知部は、第1電源スイッチのオンにより上昇する内部電源電圧を受けて動作する回路を含む。検知部は、内部電源電圧が第1電圧を超えることにより、内部回路の内部ノードが初期状態に設定されたことを検出したときに第2電源オン信号を活性化する。

(もっと読む)

スイッチ回路

【課題】リーク電流がスイッチ回路に接続される回路に影響を与えることを抑制することが可能なスイッチ回路の提供。

【解決手段】第1の電位と第2の電位の間の接続状態をオンオフする第1のトランジスタと、該第1のトランジスタのドレインにソースが接続され、前記第1のトランジスタと略同一の特性を有する第2のトランジスタとを備え、前記第1のトランジスタをオフした時に、前記第1のトランジスタのゲート−ソース間電圧VGS1と、前記前記第2のトランジスタのゲート−ソース間電圧VGS2が略等しくなることを特徴とするスイッチ回路。

(もっと読む)

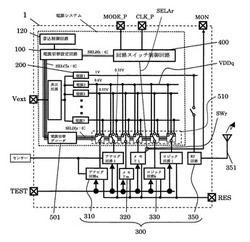

内部電位発生回路

【課題】内部電位のずれを短時間で調整することができる内部電位発生回路を提供することを課題とする。

【解決手段】内部電位発生回路は、参照電位テストモードにおいてクロック信号に同期してカウントを行う参照電位カウンタ(205)と、参照電位カウンタのカウント値に応じた参照電位を生成する参照電位発生回路(203)とを有し、第1の内部電位発生回路は、参照電位テストモードにおいて参照電位カウンタのカウントに並列してクロック信号に同期してカウントを行う第1のカウンタ(225)と、参照電位テストモードにおいて第1のカウンタのカウント値に応じて外部電位を抵抗分割した第1の比較電位を生成する第1の比較電位発生回路(223)と、第1の比較電位が参照電位発生回路により生成される参照電位より低いときには第1の内部電位を昇圧する第1の電位発生回路(226)とを有する。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】複数の基準電位を要する半導体装置、及び半導体装置の駆動において、より消費電力を軽減する。

【解決手段】電源線に直列に接続された複数の抵抗素子により、電源線に供給された電位を抵抗分割し、電源線と電気的に接続するスイッチトランジスタを介して所望の分割された電位を出力する電位分割回路を有する半導体装置であり、スイッチトランジスタのドレイン端子は出力側の回路に設けられたトランジスタのゲート端子(又は容量素子の一方の端子)と電気的に接続しノードを構成する。

(もっと読む)

半導体スイッチ

【課題】端子切替時の挿入損失の増加を抑制した半導体スイッチを提供する。

【解決手段】実施形態によれば、電源回路部と制御回路部とスイッチ部とを備えた半導体スイッチが提供される。前記電源回路部は、内部電位生成回路と第1のトランジスタとを有する。前記内部電位生成回路部は、電源線に接続され、入力電位よりも高い第1の電位を生成する。前記第1のトランジスタは、前記内部電位生成回路の入力と出力との間に接続され、前記第1の電位が前記入力電位よりも低下したときオンして前記第1の電位を前記入力電位以上に保持するようにしきい値電圧が設定されたことを特徴とする。前記制御回路部は、前記第1の電位を供給され、ハイレベルまたはローレベルの制御信号を出力する。前記スイッチ部は、前記制御信号を入力して端子間の接続を切り替える。

(もっと読む)

半導体装置

【課題】基準電圧生成回路に電源電圧が投入されてから安定平衡状態に達するまでの時間を短縮する回路を提供することを課題とする。

【解決手段】スタートアップ回路から基準電圧生成回路に入力される初期電圧を、基準電圧生成回路の安定平衡状態における内部電圧に近い電圧とすればよい。また、このような電圧を電源が遮断された状態でも保持しておくことができ、且つ起動時に出力することのできるスタートアップ回路とすればよい。

(もっと読む)

半導体集積回路

【課題】 電源ノイズを緩和しながら、内部回路が動作を開始するまでの時間を短縮する。

【解決手段】 内部回路は、基板電圧が供給されるトランジスタを含み、内部電源電圧を受けて動作する。電源スイッチは、内部回路を動作させるための電源オン信号の活性化中に外部電源線を内部電源線に接続する。基板電圧制御回路は、電源オン信号の活性化により上昇する内部電源電圧が目標電圧を超えたときに、基板電圧を第1電圧から第2電圧に変更する。第1電圧を基板電圧として受けているトランジスタのソース・ドレイン間電流は、第2電圧を基板電圧として受けているトランジスタのソース・ドレイン間電流より少ない。このため、電源スイッチがオンした後、内部電源電圧が低い期間にトランジスタのソース・ドレイン間電流を少なくでき、内部回路を流れる貫通電流を少なくできる。

(もっと読む)

半導体集積回路装置

【課題】半導体基板の表側に配置された回路が半導体基板の裏側から解析されることを検出する技術を提供することを目的とする。

【解決手段】回路ブロックが配置された第1面と、第1面の反対側の第2面とを有する半導体基板と、半導体基板を搭載する実装基板と、実装基板のうち、回路ブロックの保護対象の部分と重なる領域に配置された導電パターンと、導電パターンに改変が加えられたことを検出する検出回路とを有する半導体集積回路装置が提供される。半導体基板の第2面と実装基板とが対向するように、半導体基板が実装基板に搭載されている。

(もっと読む)

半導体集積回路装置

【課題】保護対象の回路ブロックの上に配置された導電パターンに加えられた改変の検出精度を向上するための技術を提供することを目的とする。

【解決手段】半導体基板に配置された回路ブロックと、回路ブロックのうち保護対象の部分の上層に配置された導電パターンと、導電パターンの第1部分の電位を基準電位にリセットするリセット部と、第1部分を電流供給ラインに接続する接続部と、第1部分の電位を基準電位にリセットした後に第1部分を電流供給ラインに接続してから一定時間経過後の第1部分の電圧が事前に設定された範囲に含まれるか否かを判定し、一定時間経過後の電圧が事前に設定された範囲に含まれない場合に導電パターンに改変が加えられたことを検出する検出回路とを有する半導体集積回路装置が提供される。第1部分の電圧の変化は、導電パターンの回路定数に依存する。

(もっと読む)

71 - 80 / 669

[ Back to top ]