国際特許分類[H03L7/00]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453)

国際特許分類[H03L7/00]の下位に属する分類

受動周波数決定素子からなる周波数弁別器を用いるもの (1)

周波数または位相ロックループに加えられる基準信号を用いるもの (3,073)

基準信号が発生器に直接加えられるもの (17)

周波数の基準として分子,原子または亜原子粒子のエネルギレベルを用いるもの (115)

国際特許分類[H03L7/00]に分類される特許

231 - 240 / 247

スペクトラム拡散クロックジェネレータ

【課題】設計が容易で、なおかつプロファイルの変更も簡単に行うことができるスペクトラム拡散クロックジェネレータを提供する。

【解決手段】スペクトラム拡散クロックジェネレータは、所定の単一周波数のクロックを発生するクロック源と、所定周波数の三角波を発生する三角波発生源と、三角波発生源から入力される三角波の電圧に応じて、所定の2次関数に従う2次電流を発生し、切替信号に応じて、2次電流の方向を決定する2次電流発生源と、2次電流発生源から出力される2次電流を所定のコントロール電圧に変換する電流電圧変換回路と、電流電圧変換回路によって変換されたコントロール電圧に応じて、クロック源から入力されるクロックの遅延を変え、クロック周波数がクロック毎に変動するスペクトラム拡散クロックとして出力する電圧制御ディレイラインとを備えている。

(もっと読む)

位相同期回路

【課題】 アナログ信号をデジタル信号に変換することなく、そのアナログ信号の位相を可変することができるとともに、そのアナログ信号が高周波の信号でも、そのアナログ信号の位相を可変することができるようにする。

【解決手段】 4相の信号の中から、基準信号との位相差が90度以内の2相の信号を選択するための位相検出回路5及びスイッチ部6と、その2相の信号のレベルをそれぞれ調整するレベル調整器7a,7bと、レベル調整後の2相の信号を合成する合成器8とを設け、その合成器8により合成された信号の位相が基準信号の位相と一致するように、そのレベル調整器7a,7bによるレベルの調整具合を制御する。

(もっと読む)

周波数基準信号発生装置および発生方法

【課題】 水晶発振器を用いながらも、その突発的な周波数変化を検知し、状況によっては補正することのできる周波数基準信号の発生装置および発生方法を提供する。

【解決手段】 n個(nは3以上の整数)の例えば水晶発振器を用いた信号発生装置OSC1〜OSCnと、信号発生装置OSC1の出力信号を基準信号として出力する出力信号切換手段SWと、その基準信号を基準にして残りの信号発生装置の出力信号の周波数を検出するn−1個の周波数検出手段(ゲート信号作成回路GSG、パルスカウンタPC1〜PCn−1)を備え、その周波数検出手段の出力は外部に出力される。そして、出力信号切換手段SWは、周波数検出手段の出力に基づいて基準信号の周波数に突発的な変化があったと判断された場合に、制御信号に基づいて他の信号発生装置の出力信号を基準信号として出力するように切り換える。

(もっと読む)

クロック変換器、変調器、及びデジタル放送用送信装置

【課題】変調器に入力されるクロックが10MHzの場合でも、現用/予備両系の変調器間で波形及び位相が一致した出力信号を得る。

【解決手段】 クロック変換器20は、10MHzのクロックを2/63MHzに分周する1/315分周器21と、512/63MHzのクロックを発振し、その発振周波数を電圧信号に応じて制御するVCO24と、VCO24からの512/63MHzのクロックを1/256に分周する1/256分周器25と、両分周器21、25の出力クロックを比較しその位相差に応じて前記電圧信号となるパルス信号を出力する位相比較器23と、デジタル放送用の多重フレームの周期を示すフレーム同期信号、及び10MHzのクロックを入力し、フレーム同期信号のパルス波形を10MHzのクロックに同期して整形し、整形された信号を前記リセット信号として出力する波形整形器22とを有する。

(もっと読む)

デジタル音声調整装置

【課題】 同期信号の切替時に内部同期信号が緩やかに変化するように構成し、ノイズの発生を防止する。

【解決手段】 同期切替部13により、内外の同期信号の切替を行う。同期信号は、PLL回路を構成する位相比較器15、ローパスフィルタ16、電圧制御発振器17及び位相カウンタ18から成るPLL回路に送られる。電圧制御発振器17の出力側に同期信号カウンタ19を設け、同期信号カウンタ19と位相カウンタ18の出力を補完制御部20に接続する。補完制御部20は、周波数切替時において、位相カウンタ18のリセット、位相比較動作の停止・再開、同期切替部13からの出力信号の立ち上がりエッジの抽出などの処理を行う。補完制御部20は、一定のタイミングで同期信号カウンタ19と位相カウンタ18の出力信号の位相を比較し、両信号間の位相にずれがある場合に、位相カウンタ18のカウンタ値を−1する補正信号を出力する。

(もっと読む)

水晶発振装置

【課題】 従来の発振器では経時変化により劣化して周波数が変化した場合に、定期的に計測しなおしてゼロ調整しなくてはならなかった。そのため計測の設備を用意し、計測しながら周波数調整を行っていた。

【解決手段】 本発明では、二つの発振器のうち第二発振器は普段電源を入れず劣化させないようにし、第一発振器を常に動作させ、定期的または任意の間隔で第二発振器を動作させて、これを基準として第一発振器の周波数ずれを補正し、安定な周波数を得られる発振器としている。そして第二水晶発振器を動作させていない間にも、制御回路で過去のデータから時間当たりの補正量を算出して、周波数調整を行っている。

(もっと読む)

通信システム、通信装置、リファレンスクロック発生器、およびそのクロック発生方法

【課題】 基準クロックに障害が発生してもリファレンスクロックの出力が途切れないリファレンスクロック発生器を提供する。

【解決手段】 加算器3に入力される2つの基準クロック再生回路1a、1bの出力のうち、基準クロック再生回路1bの出力をレベル調整部2を介して振幅を調整し、異なる振幅のクロックをアナログ加算して逆相となる基準クロック再生回路1a、1bの出力が入力されても加算出力が零になることを防ぎ、その加算出力を波形整形器4を介してリファレンスクロックを生成、出力することにより入力する一方の基準クロックに障害が発生してもリファレンスクロックの出力が途切れないリファレンスクロック発生器が提供できる。

(もっと読む)

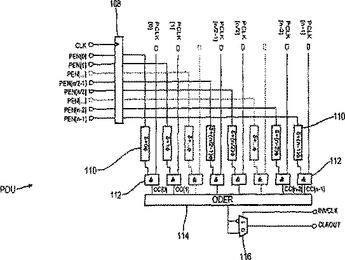

所定のクロック信号特性を有するクロック信号を生成するための方法および装置

所定のクロック信号特性を有するクロック信号(CLKOUT)を生成するための方法および装置であって、まずマスタクロック信号(CLK)に関して本質的に同一の周波数およびそれぞれ異なる位相関係を有する多数のクロック信号(PCLK[n−1:0])を準備し、次いで、準備された多数のクロック信号から(生成されるクロック信号に従って準備された制御信号(PEN[])に基づいて)所定のクロック信号を選択し、選択したクロック信号を組み合わせて所望のクロック信号(CLKOUT)を生成する。  (もっと読む)

(もっと読む)

基準クロックの周波数補正方法

【課題】コストアップを抑制し、常に安定した周波数の基準クロックを生成することができる基準クロックの周波数補正方法を提供する。

【解決手段】μcom1にて、ドライバーIC2の内蔵発振回路21の原振クロック又はその分周クロックを取得し、取得された原振クロックの周波数に関する情報を計測し、計測した周波数に関する情報に基づいて基準クロックの周波数の補正値を算出し、算出した補正値をμcom1からドライバーIC2に送信する。そして、送信されてきた補正値に基づいて、ドライバーIC2にて基準クロックの周波数を補正する。よって、高価な水晶発振子を含む水晶発振回路が不要となる。また、電源投入のタイミングを待つことなく、基準クロックの周波数を補正することが可能になる。

(もっと読む)

発振回路、及び試験装置

【課題】発振信号の連続性を保持しつつ、発振信号の位相ジッタ成分を低減することができる発振回路を提供する。

【解決手段】発振信号を生成する発振回路であって、信号を正帰還させることにより発振信号を生成する発振器と、発振信号の所定のサイクル毎に発振信号のエッジの理想タイミングでゼロクロスし、発振信号の当該エッジと同一方向の傾きのエッジを有する強制同期信号を生成する同期信号生成部と、強制同期信号を発振器の正帰還経路に注入する結合部とを備える発振回路を提供する。

(もっと読む)

231 - 240 / 247

[ Back to top ]