国際特許分類[H03L7/00]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453)

国際特許分類[H03L7/00]の下位に属する分類

受動周波数決定素子からなる周波数弁別器を用いるもの (1)

周波数または位相ロックループに加えられる基準信号を用いるもの (3,073)

基準信号が発生器に直接加えられるもの (17)

周波数の基準として分子,原子または亜原子粒子のエネルギレベルを用いるもの (115)

国際特許分類[H03L7/00]に分類される特許

131 - 140 / 247

データリカバリ方法およびデータリカバリ回路

【課題】入力データのジッタの影響を簡単な構成で低減でき、データを正確に復元できるデータリカバリ方法およびデータリカバリ回路を提供すること。

【解決手段】入力データから位相データを検出する選択信号生成部を備え、選択信号生成部が検出した位相データに基づいて入力データをサンプリングするデータリカバリ回路において、選択信号生成部は、入力データの位相と検出済みの位相データが表す位相との位相差を検出する位相差検出部530a〜530dと、位相差の絶対値が位相補正用規定値を超える場合に、位相差の絶対値が位相補正用規定値にクリップするよう位相データを補正するクリップ回路531a〜531dとを備える。

(もっと読む)

半導体装置

【課題】 シリアルデータの高速化にともなう受信性能の低下および連続同符合データ受信によるクロックデータリカバリー回路の精度低下を防止し、尚且つ消費電力の低いクロックデータリカバリー回路を提供する。

【解決手段】 シリアルデータを受信するSerDes回路101と、並走クロック信号を受信する参照SerDes回路102とを有し、SerDes回路101は、参照SerDes回路102の生成した位相制御信号P_CSを用いて位相制御された再生クロックにより受信したシリアルデータの直列並列変換を行う。

(もっと読む)

信号処理装置、信号処理方法、信号処理プログラム及びその記録媒体

【課題】 入力信号に精度良く同期した信号を迅速に生成する。

【解決手段】

直交信号生成部110Aが、信号源910からの信号SIAに含まれる角周波数ωCのパイロット信号の位相を反映し、互いの直交化が図られた信号PSA1,PSA2を生成する。これらの信号PSA1,PSA2に基づいて、位相算出部120Aが、パイロット信号の位相を算出する。こうして算出されたパイロット信号の位相に基づいて、基準信号生成部130Aが、パイロット信号と所定関係にある基準信号BSAを生成する。そして、基準信号BSAを利用して、信号加工部140が、信号SIAを加工する。

(もっと読む)

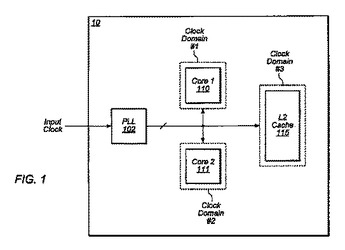

クロックサイクルスチールのための方法および装置

複数のクロック信号を生成するための方法。前記方法は、位相ロックループ(PLL)を使用して基準クロック信号を生成するステップを有する。前記基準クロックが、複数のクロック分周器ユニットのそれぞれに供給され、前記複数のクロック分周器ユニットのそれぞれが、前記受信基準クロック信号を分周して、対応する分周クロック信号を生成する。前記方法は、前記対応する受信分周クロック信号の周波数と、除去するサイクル数とに基づいて、それぞれが有効周波数を有する複数のドメインクロック信号を生成するために、(所定の数のサイクルにつき)1以上のクロックサイクルを除去する。  (もっと読む)

(もっと読む)

遅延回路およびそれを用いた信号発生回路

【課題】 プログラマブル遅延回路のオフセット遅延時間が周囲温度などの周囲条件によって変化するので、このプログラマブル遅延回路を用いた信号発生回路の出力波形信号が不安定になってしまうという課題を解決する。

【解決手段】 プログラマブル遅延回路と遅延回路を直列接続してプログラマブル遅延回路にクロックを入力し、この2つ遅延回路の合計遅延時間が一定になるように前記プログラマブル遅延回路の遅延時間を制御すると共に、このプログラマブル遅延回路の出力を複数のプログラマブル遅延回路に入力するようにした。また、この複数のプログラマブル遅延回路を用いて信号発生回路を構成した。周囲条件が変化しても複数のプログラマブル遅延回路のクロックに対する遅延時間が変動することがない。

(もっと読む)

クロックデータ再生回路

【課題】高速シリアルデータ転送の受信回路において、低消費電力モードから通常モードに復帰する際の復帰時間を短縮する。

【解決手段】シリアルデータ転送路から転送される同期用クロックを含むシリアルデータから同期用クロック及びデータを再生するクロックデータ再生回路であって、シリアルデータ及び基準クロックを電力モードに応じて選択してクロックデータ再生回路に供給する選択回路を具備する。

(もっと読む)

可変タイミングメモリ

【課題】同期回路装置の設計に於いて、タイミング最適化の作業工程を削減化する。

【解決手段】同期回路装置10内の可変タイミングメモリ20のモジュールは、メモリアレイ21とその入出力メモリ制御回路22,23に加えて、クロック端子Tに入力したクロック信号CLKを遅延する信号線24と、クロック信号CLKをそのまま伝送する信号線25と、両信号線24,25を入力とするセレクタSL1と、メモリライト/リード信号が印加され且つセレクタSL1のセレクト端子と繋がったタイミングモード端子TMTとを有する。セレクタSL1は、メモリライト信号の受信に応じて信号線24を選択し、遅延されたクロック信号を入出力メモリ制御回路22,23に印加する。他方、メモリリード信号の受信に応じてセレクタSL1は信号線25を選択し、クロック信号CLKをそのまま入出力メモリ制御回路22,23に印加する。

(もっと読む)

パルス無線受信装置および同期方法

【課題】NRZ符号化されたパルス信号に対しても同期可能であり、かつ従来のEarly/Late DLL方式に比べフィンガー数を削減したパルス無線受信装置および同期方法を提供する。

【解決手段】相対差算出手段1505は、最大値検出手段1551A、1551Bと最小値検出手段1552A、1552Bおよび加算手段1553A、1553B、1554を備える。最大値検出手段1551Aは、サンプル手段1504から入力される連続したn個のサンプル値1504Aから最大値を検出し最大値Amaxを出力する。同期制御手段1506は、相対差算出手段1505からの相対振幅差信号iVをもとに包絡線信号とク

ロック信号のタイミングが同期するように、クロック信号の位相を制御する遅延制御信号を生成し、遅延手段1503へ出力する。

(もっと読む)

受信装置

【課題】サンプラブロック回路におけるシリアルデータ信号とサンプリングクロック信号との間の動作マージンを確保することができる受信装置を提供する。

【解決手段】受信装置1では、位相調整回路50により位相調整されたクロック信号に基づいて、サンプリングクロック信号生成回路40により、多相のサンプリングクロック信号が生成される。サンプラブロック回路30nにより、サンプリングクロック信号が指示するタイミングでシリアルデータ信号の各ビットのデータがサンプリングされて出力される。位相調整回路50におけるクロック信号の位相調整量は、サンプリングクロック信号生成回路40において多相のサンプリングクロック信号が生成されてから、サンプラブロック回路30nにおいて該サンプリングクロック信号がサンプリングタイミングを指示するまでの遅延時間を相殺するよう設定される。

(もっと読む)

クロック分配回路およびそれを用いたインターフェース装置

【課題】データの伝送速度および信頼性の低下を防止できるようにしたクロック分配回路およびそれを用いたインターフェース装置を提供する。

【解決手段】入力されたクロックを制御電圧によって可変とされた遅延を有するようにして分配クロックとして出力する電圧制御分配手段、及び前記データと前記分配クロックの位相差を用いて前記制御電圧を生成する制御電圧生成手段を備える。

(もっと読む)

131 - 140 / 247

[ Back to top ]