国際特許分類[H03L7/00]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453)

国際特許分類[H03L7/00]の下位に属する分類

受動周波数決定素子からなる周波数弁別器を用いるもの (1)

周波数または位相ロックループに加えられる基準信号を用いるもの (3,073)

基準信号が発生器に直接加えられるもの (17)

周波数の基準として分子,原子または亜原子粒子のエネルギレベルを用いるもの (115)

国際特許分類[H03L7/00]に分類される特許

141 - 150 / 247

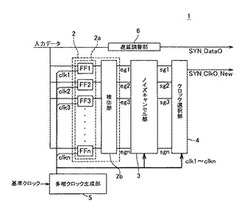

クロックリカバリ回路

【課題】シリアル伝送されるデータにノイズが混入しても、そのノイズの影響を少なくすることができるクロックリカバリ回路を提供する。

【解決手段】基準クロックから多相クロック生成部5で生成された多位相クロックのうち、入力されたシリアルデータの変化点の中間(真中)に立ち上がりがあるクロックを選択して出力するクロックリカバリ回路1において、入力データのエッジを検出した後に、所定以下の信号幅のノイズ成分を除去するノイズキャンセル部3を設け、ノイズ成分によるクロックの切替えが起らないようにしてクロック選択部4へ出力する。

(もっと読む)

クロック信号生成回路、及び半導体装置

【課題】製造プロセスにおけるばらつきが原因による同期期間や同期期間終了後の自走期間において、周波数が変動することがなく、安定した動作を実現し、また安価な半導体装置を提供する。

【解決手段】第1の基準クロック信号を生成する基準クロック信号生成回路と、第1基準クロックの信号及び同期信号を用いて第1の基準クロック信号の立ち上がりのエッジ数を計数する第1のカウンタ回路と、第1のカウンタ回路の計数値を用いて第1の基準クロック信号の立ち上がりのエッジ数を計数する第2のカウンタ回路と、第1のカウンタ回路の計数値を用いて第1の基準クロック信号を分周し、第2の基準クロック信号を生成する第1の分周回路と、第2の基準クロック信号を分周し、クロック信号を生成する第2の分周回路と、を有するクロック生成回路を半導体装置に搭載する。

(もっと読む)

半導体装置

【課題】半導体制御装置において、供給先別にクロックの位相を制御し、且つクロック供給の供給先別優先順位を制御することによって、動作時の電源電圧変動を抑えこれにより動作時の消費電力を抑える。

【解決手段】機能により複数に分割された機能モジュールと、上記機能モジュールの夫々に供給されるクロック信号を生成するクロック発振回路と、外部から入力される上記機能モジュールの夫々に対するクロック供給イネーブル信号に従って、上記クロック発振回路の生成するクロック信号を上記機能モジュールの夫々に供給するクロック制御回路を含む半導体装置を提供する。

(もっと読む)

クロック供給装置

【課題】上位からのクロックに位相同期したクロックを供給するクロック供給装置に関し、現用系と予備系とのクロックの位相を一致させる。

【解決手段】システムクロックに位相同期した現用系クロックを出力する現用系システムクロック供給装置1aと予備系クロックを出力する予備系システムクロック供給装置1bとを有し、システムクロックに位相同期したクロックを出力するDPLL部2a,2bと、このDPLL部2a,2bからのクロックを遅延制御する可変遅延回路4a,4bと、この可変遅延回路4a,4bを介して出力する現用系クロックと予備系クロックとの位相を比較する位相比較部7a,7bと、この位相比較部7a,7bによる現用系クロックと予備系クロックとの位相比較結果により、可変遅延回路4a,4bの遅延量を制御する位相比較判定部5a,5bとをそれぞれ備えている。

(もっと読む)

内部クロック発生回路を備えた半導体記憶装置

【課題】 半導体記憶装置においてはユーザー要求により、外部クロックの入力パッドの配置位置と、コマンド信号の入力パッド及びコマンドデコーダの配置位置とが離れることがある。このためコマンドデコーダでのコマンド取り込みが遅れるという問題がある。

【解決手段】 コマンドデコーダに入力されるクロックを、DLL回路を備えた内部クロック発生回路により発生させる。内部クロック発生回路からの内部クロックを入力されたコマンドデコーダは、外部クロックに同期した最速のタイミングで内部コマンド信号を出力できる。さらにDCC判定回路を備えることで、デューティを調整することもできる。コマンドデコーダ用の内部クロック発生回路を備えることで、高速アクセス可能な半導体記憶装置が得られる。

(もっと読む)

クロック再生装置

【課題】安定した高速動作が可能なクロック再生装置を提供する。

【解決手段】クロック再生装置1は、受信データD1からデータ受信用の再生クロックCK1を得るものであって、受信データD1のレベルが所定のレベルである場合に、受信データD1に同期した所定周波数の信号S1を出力する発振器21と、発振器21に直列に接続され、信号S1のレベルが所定のレベルである場合に、信号S1に同期した所定周波数の信号S1を再生クロックCK1として出力する発振器22とを備える。

(もっと読む)

クロック制御回路、集積回路装置及び電子機器

【課題】ノイズフィルタでは完全には除去することができないようなノイズがクロック信号に発生した場合でも、このクロック信号で動作する回路の誤動作を防止することができるクロック制御回路を提供すること。

【解決手段】クロック制御回路10は、発振クロック22の電圧が所定の範囲にあるか否かを判断し、発振クロック22の電圧が所定の範囲にない時はノイズ検出信号128を生成するノイズ検出回路120と、ノイズ検出信号128に基づいて、少なくとも所定の期間、クロック出力停止信号138を生成するクロック出力停止信号生成回路130と、発振クロックを所定の時間遅延させた遅延クロック信号148を生成する遅延クロック生成回路140と、クロック出力停止信号138が存在する期間は、遅延クロック信号148の外部への出力を停止するように制御するクロック出力停止制御回路150と、を含む。

(もっと読む)

位相補償クロック分周回路

【課題】分周クロックが同期信号に対して常に同一位相となるように制御し誤動作や動作遅れを防止する位相補償クロック分周回路を提供する。

【解決手段】所定周期の源クロックを動作クロックとする第1部品1と、源クロックを分周した分周クロックを動作クロックとし第1部品1と同期した処理を行う第2部品2とが混在するシステムで用いられる位相補償クロック分周回路において、源1クロックを発生し第1部品1に出力するクロック発生手段3と、源クロックを分周して生成した分周クロックを第2部品2に出力する分周手段4と、第1部品1が源クロックから生成し第2部品2に出力する同期信号を取り込み該同期信号のパルスエッジから所定の一定期間だけ遅延させた時点に位相を合わせた分周クロックを分周手段4に発生させる同期制御手段5とを備える。

(もっと読む)

デジタル制御発振器、このデジタル制御発振器を備えた位相同期ループ及び通信機

【課題】スプリアスが生じにくい。

【解決手段】ADCから入力されたnビットのデジタル信号は、mビットが整数部41、且つ、n−mビットがデジタル制御値時間変化部43に入力される。そして、デジタル制御値時間変化部43から時間的に変化するデジタル制御値が小数部42に入力される。デジタル制御発振器4は、整数部41によってステップ周波数刻みで発振周波数を変化させる。また、小数部42によってステップ周波数よりも小さな周波数刻みで発振周波数を変化させる。このとき、小数部42によって変化させることができる周波数は、ステップ周波数よりも大きい。

(もっと読む)

タイマ回路及びプログラム

【課題】本発明は携帯装置等のタイマ回路及びプログラムに関し,低周波数(32KHz )の水晶発振子を使用しても長時間の計時を行っても誤差の累積を防ぐことを目的とする。

【解決手段】低周波数の水晶発振子の出力をカウントしてほぼ1ミリ秒毎の出力を発生する第1のカウンタと,該カウンタの出力をカウントしてmミリ秒毎の出力を発生する第2のカウンタと,第2のカウンタの出力を処理装置に供給するタイマ回路であって,第1のカウンタを「32」または「33」のカウント容量の一方でカウントするよう切替える切替回路を設け,第2のカウンタのカウント値が予め設定した分散した多数の値の一つと一致するか判別して切替指示を発生する調整判別回路を備え,切替指示により第1のカウンタのカウント値を切替えることにより,時計回路との誤差が補正された信号が第2のカウンタから出力するよう構成する。

(もっと読む)

141 - 150 / 247

[ Back to top ]