国際特許分類[H03L7/00]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453)

国際特許分類[H03L7/00]の下位に属する分類

受動周波数決定素子からなる周波数弁別器を用いるもの (1)

周波数または位相ロックループに加えられる基準信号を用いるもの (3,073)

基準信号が発生器に直接加えられるもの (17)

周波数の基準として分子,原子または亜原子粒子のエネルギレベルを用いるもの (115)

国際特許分類[H03L7/00]に分類される特許

161 - 170 / 247

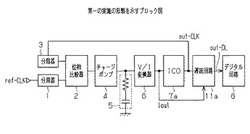

PLL回路

【課題】帰還ループに遅延回路を挿入することなく、出力信号でのジッタの発生を抑制し得るPLL回路を提供する。

【解決手段】基準信号ref−CLKと帰還信号の位相を比較する位相比較器2と、チャージポンプ4と、ループフィルター5と、電圧電流変換器6と、電流制御発振器7aと、電流制御発振器の出力信号を分周して帰還信号を生成する分周器3とを備えた帰還ループにより、出力信号out−CLKの周波数を基準信号で設定される周波数に収束させるPLL回路であって、電流制御発振器7aから負荷回路8に出力される出力信号out−DLと位相比較器2に入力される基準信号の位相をずらす遅延回路11aを帰還ループ外に備えた。

(もっと読む)

クロックデータ復元装置

【課題】より正確にクロック信号およびデータを復元することができるクロックデータ復元装置を提供する。

【解決手段】クロックデータ復元装置1は、入力したデジタル信号に基づいてクロック信号およびデータを復元する装置であって、イコライザ部10、サンプラ部20、クロック生成部30、イコライザ制御部40および位相モニタ部50を備える。イコライザ部10、サンプラ部20およびイコライザ制御部40によるループ処理により、イコライザ部10におけるデジタル信号のレベル調整量の制御が行われるが、一方で、クロック信号CKとデジタル信号との間の位相差が所定値より大きいときには当該制御が位相モニタ部50により停止される。これにより、より正確にクロック信号およびデータが復元され得る。

(もっと読む)

マイクロ波発生装置

【課題】マイクロ波発生装置の複数の出力間の位相を連続的に変化させることのできる位相可変手段を着脱自在な構造体として提供する。

【解決手段】マイクロ波発生装置10の分配部12と初段増幅部13aを接続するマイクロ波伝送路14aの両端部(点A、点B)に接続される位相可変手段21は、入力部22と出力部23とを接続するジグザグ形状のマイクロ波伝送路24と、マイクロ波伝送路24の所定領域を覆う半円形状の誘電体板28を備え、誘電体板28をマイクロ波伝送路24に摺動回転させてマイクロ波伝送路24を伝送するマイクロ波の位相を遅延させる。そして、位相可変手段21における位相遅延量の連続的変化はマイクロ波発生装置10の2つの出力の位相差に反映され、このような位相差が変化する2つのマイクロ波信号を加熱装置に適用することで様々な被加熱物の加熱の均一化を促進させることができる。

(もっと読む)

複数クロック間位相調整装置

【課題】従来の非同期データ受け渡しでは、送り側の信号変化周期を受け側の動作クロックの2倍以上にしておく必要があった。

ここで本発明では、この制限なく、非同期データの受け渡しを可能にすることを目的とする。

【解決手段】この目的を達成するために本発明では、非同期の関係にある2つのクロックから位相差量をパルス幅で抽出し、これを制御カウンタのクロックとして使用し、徐々にパルス幅が大きくなってカウンタが動作すると、遅延量制御部によって、一方のクロックの遅延量を制御し、一方のクロックが他方のクロックに追従する装置を提供する。

(もっと読む)

移相回路

【課題】 移相量を常に一定に制御可能とし、電源電圧変動時等の影響の低減、素子バラツキの影響を低減する移相回路の提供。

【解決手段】基準周波数信号が入力されて2分配され一方の信号は位相比較器102の一方の入力となり、他方の信号は移相器101を介してその位相が移相された後に、前記位相比較器102の他方の入力となり、位相比較器102の出力はループフィルタ(LPF)103を介して差動増幅器104の一方の入力端子に入力され、差動増幅器104の出力信号により移相器101の移相量が制御されるPLLループを有し、差動増幅器104の他方の入力端子に印加される基準電圧により前記移相器101での移相量が定まる。

(もっと読む)

標準信号発生器及び標準信号発生システム

【課題】恒温設備を設けることなく位相ドリフトを低減させて、標準信号発生器のウォームアップ時間の短縮を図ること。

【解決手段】位相補正データ生成部4のA/D変換器41は、基準信号生成部1から出力された基準信号14aの周波数をサンプリング周波数として標準信号100aをA/D変換する。プログラマブル周波数ディバイダ42が分周した基準信号14aの周期で、データ間引き部43はA/D変換器41からのビート信号41aを間引き抽出する。補正量算出部40は、データ間引き部43からのビート信号43aの電圧値に基づいて、位相ドリフト量Δθdriftを算出する。その位相ドリフト量Δθdriftに基づいて標準信号100aの位相補正を行う。

(もっと読む)

半導体装置

【課題】 クロック信号の高い周波数精度およびシステムの低消費電流を実現することができる半導体装置を実現する。

【解決手段】 本発明の半導体装置は、外付けされる外部発振回路17の発振動作を発振停止信号により制御し、外部発振回路17からの信号を外部クロック信号として出力する制御回路11と、クロック信号を生成し出力する内部発振回路12と、外部クロック信号または内部発振回路12からのクロック信号を切り替え信号に基づいて選択し、内部クロック信号として出力するセレクタ14を有する。

(もっと読む)

位相調整回路及びフェイズロックドループ回路

【課題】周波数の高いクロックを用いる事無く、小さな回路規模で実現でき、より細かい分解能で位相調整することができる位相調整回路及びフェイズロックドループ回路を提供する。

【解決手段】入力される水平同期信号SYNC_INは、位相シフト回路21により位相調整データCKPHASEの上位2Bitsの値に応じてシフトされ、その出力によりアップダウンカウンタ22はクロックNCKPをアップ及びダウンカウントして、逓倍回路32等経てラッチ回路23に出力し、ラッチ回路23は、データイネーブル用パルスENCKPによりラッチして、位相調整出力HD_SIGを出力する。

(もっと読む)

半導体集積回路

【課題】PLL(Phase Locked Loop)回路を搭載した半導体集積回路において、当該PLL回路の発振安定待ちの時間を有効利用する。

【解決手段】実動作準備期間中に、PLL回路50の帰還ループを遮断した状態で位相比較器51の参照クロック入力部Fpと帰還クロック入力部Frとの双方に基準クロック100を供給して、位相比較器51における位相差の検出不感帯が小さくなるように当該位相比較器51内のリセット信号の遅延を調整する。

(もっと読む)

半導体集積回路およびそれを備えた電子機器

【課題】発振信号を安定して生成することが可能な半導体集積回路およびそれを備えた電子機器を提供する。

【解決手段】半導体集積回路101は、発振信号を出力する発振回路1と、発振回路1から受けた発振信号を外部へ出力するか否かを切り替える切り替え回路2とを備える。

(もっと読む)

161 - 170 / 247

[ Back to top ]