国際特許分類[H03L7/00]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453)

国際特許分類[H03L7/00]の下位に属する分類

受動周波数決定素子からなる周波数弁別器を用いるもの (1)

周波数または位相ロックループに加えられる基準信号を用いるもの (3,073)

基準信号が発生器に直接加えられるもの (17)

周波数の基準として分子,原子または亜原子粒子のエネルギレベルを用いるもの (115)

国際特許分類[H03L7/00]に分類される特許

171 - 180 / 247

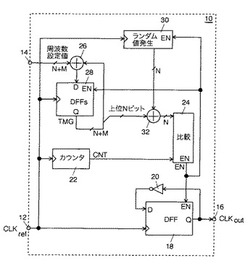

クロック発生回路

【課題】

サイドバンドを低減する。

【解決手段】

カウンタ22は、基準クロックCLKrefをカウントし、カウント値CNTを比較回路24に印加する。加算器26は、入力端子14からの周波数設定値にN+MビットのDFF28のQ出力を加算し、加算結果をDFF28のD入力に印加する。DFF28は、比較回路24からのイネーブル信号ENと基準クロックCLKrefの立ち上がりと立ち下がりに従い、加算器26の出力をラッチする。加算器32は、ランダム値発生回路30からのランダム値をDFF28のQ出力の上位Nビットに加算し、加算結果を比較回路24に印加する。比較回路24は、両入力が等しいときにイネーブル信号を出力する。インバータ20によりQ出力がD入力に帰還接続されるDFF18は、イネーブル信号と基準クロックCLKrefに従いQ出力をハイからロー又はその逆に遷移する。

(もっと読む)

クロック同期回路及びそれを備えた半導体装置

【課題】複数の回路間で異なるクロックを使用した場合であっても、安定した通信が可能であるクロック同期回路及びそれを備えた半導体装置の提供を課題とする。

【解決手段】受信したデータの変化点を検出し、リセット信号を出力する手段と、クロック信号を出力する基準クロック発生回路と、クロック信号をカウントする基準クロックカウンター回路と、基準クロックカウンター回路から出力された信号を分周する分周回路と、分周回路から出力された信号により回路動作用基準クロック信号を出力する手段とを設ける。

(もっと読む)

二重システム型基準周波数信号発生器

【課題】簡素な構造でありながら、切り替え時に基準周波数信号の位相ズレを殆ど生じない二重システム型基準周波数信号発生器を提供する。

【解決手段】現用機モードの基準信号発生部1Aは、GPS衛星1PPS信号S1PAに基づいて位相制御し、基準周波数信号SfAと基準1PPS信号S1PAを生成する。出力選択部2は、現用機モードの基準信号発生部1Aの基準周波数信号SfAと基準1PPS信号S1PAを後段のシステム機器100に出力する。予備機モードの基準信号発生部1Bは、現用機モードの基準信号発生部1Aの基準1PPS信号S1PAに基づいて位相制御し、基準周波数信号SfBと基準1PPS信号S1PBを生成する。このように、予備機モードの基準信号発生部1Bが現用機モード基準信号発生部1Aの出力に対して位相同期することで位相ズレが抑圧され、切り替わり時の位相不連続が抑制される。

(もっと読む)

クロック生成回路

【課題】

要求されるデューティ比の同期クロック信号を生成できるか否かの判別が正確に行われるクロック生成回路を提供する。

【解決手段】

クロック生成回路100において、外部から入力されてきた外部クロック信号Sextclkを遅延することにより外部クロック信号Sextclkに同期した同期クロック信号Sclkを生成するDLL回路110と、DLL回路110のデューティ比劣化テスト用にパルス幅を変化させたテスト信号Stestを生成するテスト信号生成回路120と、外部クロック信号Sextclkおよびテスト信号Stestのうちの一方の信号を選択してDLL回路110に入力する選択回路130とを備えたことを特徴とする。

(もっと読む)

主にデジタルな時間基準発生器を使用する信号完全性測定のシステム及び方法

1以上の被テスト信号のサンプリングを制御するための、独自の時間基準発生技法を利用する信号完全性測定のシステム及び方法である。本開示に従い作成した時間基準発生器は、位相フィルタ及び変調回路を備えており、これらは、シグマデルタ変調器の出力の関数として、高速に変化する位相信号を発生させるものである。この位相フィルタは、該高速に変化する位相信号から所望でない高い周波数の位相成分をフィルタする。フィルタされた該信号は、1以上のサンプラをクロックするために使用され、それによって上記の被テスト信号のサンプリングの事例を生成する。次に、これらサンプリングの事例を、被テスト信号の種類に適した何らかの1以上の様々な技法を使用して分析する。 (もっと読む)

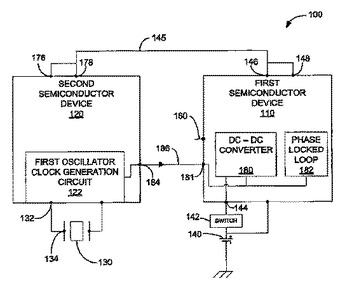

半導体デバイス及び水晶発振体を共有するシステム並びに方法

システムは、第1の半導体デバイス、第2の半導体デバイス、及び外部水晶発振器を含む。第1の半導体デバイスは、電源電圧出力及び外部ピン入力を含む。第1の半導体デバイスは、電源電圧出力を提供する直流−直流(DC-DC)変換回路を含む。第2の半導体デバイスは、第1の半導体デバイスの電源電圧出力に接続された電源電圧入力とクロック信号出力とを含む。外部水晶発振器は、第2の半導体デバイスを介して第1の発振クロック発生回路に接続されている。  (もっと読む)

(もっと読む)

CDR回路およびデューティ比制御回路

【課題】入力データのデューティ比が崩れている場合であっても、正規のデータを再生できるようにしたCDR回路を提供する。

【解決手段】データ入力端子10より入力された入力データからクロックを再生するクロック再生手段50と、制御電圧入力端子60に入力された電圧によって前記入力データの遅延時間を可変して出力する可変遅延手段30Aと、クロック再生手段50から出力されるクロックを用いて可変遅延手段30Aの出力データを保持し再生データ出力端子20に出力するデータ保持手段40と、を有する。

(もっと読む)

無線測定装置

【課題】 温度、圧力又は湿度等が広範囲に変化する環境下においても、測定データの無線送受信に用いる周波数を安定させ、確実かつ安定した状態で測定データを無線送信できるようにする。

【解決手段】 送受信部17は既知の受信電波の周波数に合わせた周波数の搬送波に基づく電波をその外部機器に送信する。第1の測定部13は該装置本体9内の温度を測定する。第2の測定部15は装置本体9外の環境雰囲気に係る変化量を測定する。第1の補正部13は第1の測定部23による測定温度の変化範囲に応じて内部発振信号の周波数を受信電波の周波数に近づけるよう第1の補正をする。第2の補正部25は第1の補正がされた内部発振周波数に対し受信電波の周波数に合わせるように第2の補正をして搬送波を形成する。送受信部17は第2の測定部15からの測定データを搬送波に乗せて電波を送信する。

(もっと読む)

クロック生成回路、情報再生装置、電子機器及びクロック生成回路の設計方法

【課題】 PLLを用いることなく、低コスト且つ低消費電力で、複数のクロックを生成するクロック生成回路、情報再生装置、電子機器等を提供する。

【解決手段】 クロック生成回路200は、周波数fHを有する入力クロックiclkに基づいて、第1の出力クロック及び周波数f0を有する第2の出力クロックを生成する。クロック生成回路200は、前記入力クロック又は該入力クロックを間引いたクロックを第1の分周比d1(d1は正の整数)で分周した前記第1の出力クロックを生成する第1の分周カウンタと、前記第1の出力クロックを第2の分周比d2(d2は正の整数)で分周し前記第2の出力クロックを生成する第2の分周カウンタと、前記第2の出力クロックに基づいて、前記第1の分周カウンタで分周される前記入力クロックの間引き制御を行う間引き制御部とを含む。

(もっと読む)

デジタル放送受信装置およびデジタル放送システム

【課題】本発明は、可変周波数の水晶発器(VCXO)を用いること無く、基地局と受信装置間の時間情報および基準クロックの同期を実現することができる、デジタル放送受信装置等を提供する。

【解決手段】水晶発振子22は、所定の固定周波数のクロックを発振する。可変デジタル分周回路24は、固定周波数を分周比によりデジタル分周し、分周比を変更することができる。システムでコーダ5は、基地局からの基準時間情報を検出する。基準カウンタ18は、受信装置20の時間情報を生成する。位相比較器13は、基準時間情報と時間情報との差分を検出する。分周比制御回路25は、前記差分に基づいて前記分周比の変更を制御する。また、基準カウンタ18は、可変デジタル分周回路24により分周された周波数を有するクロックに基づいて時間情報の生成を行い、時間情報を位相比較器13にフィードバックさせている。

(もっと読む)

171 - 180 / 247

[ Back to top ]