国際特許分類[H03L7/00]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453)

国際特許分類[H03L7/00]の下位に属する分類

受動周波数決定素子からなる周波数弁別器を用いるもの (1)

周波数または位相ロックループに加えられる基準信号を用いるもの (3,073)

基準信号が発生器に直接加えられるもの (17)

周波数の基準として分子,原子または亜原子粒子のエネルギレベルを用いるもの (115)

国際特許分類[H03L7/00]に分類される特許

211 - 220 / 247

位相制御装置、周波数制御装置、発振装置、位相制御方法及び周波数制御方法

【課題】

DDSなどの発信源の位相をより多彩に制御すること。

【解決手段】

本発明の位相制御装置は、所定の信号を、この信号の位相を示す第1の位相情報に基づいて出力する複数の信号源から出力される信号間の位相を制御する位相制御装置であって、複数の信号源ごとに設けられ、信号源から出力される信号の位相を示す第2の位相情報を格納する複数の位相情報格納手段と、位相情報格納手段によって格納された第2の位相情報に基づいて、複数の信号源のうち少なくとも1つの信号源から出力される信号の位相を変えて前記複数の信号源から出力される信号間の位相差を制御する位相制御手段とを具備する。また、第2の位相情報を第1の位相情報より高分解能となるよう構成することができる。

(もっと読む)

局間補正装置

【課題】電圧制御水晶発振器の使用を回避することにより、コストの削減及び消費電力の低減を図ることができるとともに、視聴者が違和感を感じることなく送信局と受信局との映像・音声信号の同期をとることが可能な、局間補正装置を得る。

【解決手段】比較器6は、カウンタ値K1,K3の差Y3が許容値Mを超えたことを検出すると、補正実行命令S4,S5を出力する。補正実行命令S4は補正部2に入力され、補正部2は、デコード部1から出力されたデータD2に対してリニアスケーリング補正を行って、補正後のデータD3を出力する。また、補正実行命令S5は自走PCRカウンタ5に入力され、自走PCRカウンタ5は、補正部2によるリニアスケーリング補正の補正量に応じて、カウンタ値K3を補正する。

(もっと読む)

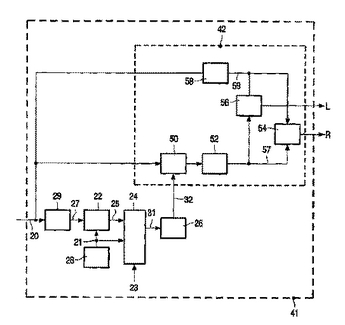

信号発生装置

【課題】信号発生装置の複数のチャンネルに供給されるクロックを停止することなく、チャンネル間の出力信号位相を制御する。

【解決手段】第1及び第2チャンネル20及び22は、クロック位相シフト回路26及び28と、メモリ、並直列変換回路、DACを有する信号発生ブロック10及び12を具えている。位相比較回路24は、信号発生ブロック10及び12内のメモリから波形データを読み出すための分周クロックを受けて、これらの位相を比較し、位相差信号を生成する。CPUは、この位相差信号を用いてクロック位相シフト回路26及び28を制御し、信号発生ブロック10及び12に供給するクロックの位相シフトを行うことで、第1及び第2チャンネル20及び22の出力信号の位相関係を所望の関係に制御する。

(もっと読む)

クロック生成回路

【課題】 クロック切り替え時において、現状の基準分周クロックと切り替わり先の基準分周クロックの信号レベルや、比較分周信号の信号レベルに関わらず、クロック切り替え時の異常を回避することができ、更に入力基準クロックに用いる周波数の制限を大幅に緩和することができる、PLL回路を有したクロック生成回路を得る。

【解決手段】 入力クロックCLK1とCLK2との切り替わり直後に第1及び第2の各基準分周回路16,17と第1及び第2の各比較分周回路19,20をそれぞれリセットすると共に、第1の選択回路15から出力された基準選択クロックSEL1と第2の選択回路18から出力された比較選択クロックSEL2にパルス信号Cをそれぞれ加えてPLL回路11に入力するようにした。

(もっと読む)

クロック同期装置及びそれに用いるクロック同期方法

【課題】 二つの出力クロック間の位相関係を一定とし、二つの出力クロック間の位相ズレの発生を防ぐことが可能なクロック同期装置を提供する。

【解決手段】 初期状態がデフォルトで基準クロック信号REFnをリファレンスクロックとする場合、同期マスタ制御部11はREF選択回路(n)12の選択信号SELnの出力制御として基準クロック信号REFnを選択し、REF選択回路(e)13の選択信号SELeの出力制御として同期回路(A)14の出力信号n1を選択する。出力切替制御部16によって切替制御が行われ、クロック出力は出力n1から出力e1への選択に切替わる時、同期マスタ制御部11はREF選択回路(n)12の選択信号SELnの出力制御として基準クロック信号REFnの選択を保持し、REF選択回路(e)13の選択信号SELeの出力制御として同期回路(A)14の出力信号n1の選択を保持する。

(もっと読む)

多重周波数源システムのためのオフセット信号位相調整

オフセット信号位相調整を用いる同調可能な多重周波数源システムが、第1の周波数源と、位相遅延素子と、第1の周波数源と同時に動作するように構成された第2の周波数源とを含む。第1の周波数源は、基準入力信号を受け取るように結合された入力と、第1の周波数源信号を提供する出力とを含む。位相遅延は、入力基準信号を受け取るように結合された入力と、出力とを含み、位相遅延素子は、入力基準信号に既定の位相遅延を適用して位相遅延入力信号を生み出すように動作する。第2の周波数源は、位相遅延入力信号を受け取るように結合された入力と、第2の周波数源信号を提供する出力とを含む。 (もっと読む)

クロック生成器及びこれを用いた無線受信装置

【課題】クロック信号の分配のために長い配線を引き回す必要がなく、しかも同一周波数のクロック信号間で位相を揃えることができるクロック生成器を提供する。

【解決手段】共通の基準信号源11からの基準信号を受けて周波数の異なる複数のクロック信号群をそれぞれ発生する複数のフェーズロックドループ12−1〜12nを有するクロック生成器10は、基準信号の位相と帰還信号との位相差に応じた電圧信号を発生する位相比較器13−1〜13nと、位相比較器13−1〜13nからの電圧信号によって制御されるVCO15−1〜15−nと、VCO15−1〜15−nの出力から位相比較器13−1〜13nの帰還信号入力までの帰還経路内に縦続接続される分周器群D1〜Dm群を有し、分周器群D1〜Dmの各々の出力からクロック信号群を取り出す。

(もっと読む)

位相同期ループを用いない信号の回復

デジタル入力信号(20)から第1のデジタル信号(7、31)を回復するための構成が、デジタル入力信号(20)をフィルタリングするためのデジタル・フィルタ(29)と、デジタル基準信号(21)を生成するためのデジタル制御発振器28と、フィルタリングされたデジタル入力信号(27)とデジタル基準信号(21)との位相差(25)を求めるためのデジタル位相検出器(22)とを備える。第1のデジタル信号(7、31)は、求められた位相差(25)を、デジタル基準信号(21)の位相に加えることによって回復することができる。  (もっと読む)

(もっと読む)

電圧制御水晶発振器を同調させるための値を動的に計算するための方法及びシステム

同調電圧によって制御可能な状態の電圧制御水晶発振器(VCXO)である。該VCXOは、水晶と、調整可能なコンデンサアレイとを有する。一例において、該VCXOは、前記同調電圧を対応するディジタル値に変換するアナログ−ディジタル変換器と、前記水晶及び同調プロファイルにおける1つか又は複数のパラメータを格納するメモリと、論理ブロックとを備える。該論理ブロックは、前記ディジタル値と前記水晶及び同調ファイルにおける1つか又は複数のパラメータとを受け取って、前記調整可能なコンデンサアレイを調整することにおいて使用するための1つか又は複数の値を動的に算出する。このようにして、前記論理ブロックは、リアルタイムに、前記VCXOの動作(すなわち、発振周波数)を動的に計算し且つ調整することができる。  (もっと読む)

(もっと読む)

タイミングリカバリ回路及び間引きクロック生成方法

【課題】 本発明は、クロック信号の間引き処理にともなう特性劣化を防止したタイミングリカバリ回路及び間引きクロック生成方法を提供することを目的とする。

【解決手段】タイミングリカバリ回路は、第1のタイミング信号を出力端に出力する第1の発振回路と、第2のタイミング信号を出力端に出力する第2の発振回路と、第1のクロック信号の供給端と第1の発振回路の出力端とに結合され第1のタイミング信号に応じて第1のクロック信号のパルスを間引いた第2のクロック信号を出力端に出力する第1の間引き回路と、第1の間引き回路の出力端と第2の発振回路の出力端に結合され第2のタイミング信号に応じて第2のクロック信号のパルスを間引いた第3のクロック信号を生成する第2の間引き回路を含み、第1のタイミング信号及び第2のタイミング信号の何れか一方は固定の周期を有し他方はフィードバック制御に応じた周期を有することを特徴とする。

(もっと読む)

211 - 220 / 247

[ Back to top ]