国際特許分類[H03L7/081]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 付加的な制御移相器を有するもの (308)

国際特許分類[H03L7/081]に分類される特許

11 - 20 / 308

遅延ロックループ回路及びロックアップ方法

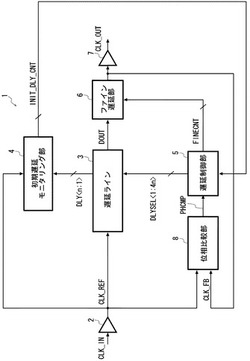

【課題】レイアウト面積の増加を抑えつつロックアップ時間の高速化を実現する。

【解決手段】本発明に係る遅延ロックループ回路1は、遅延ライン3と、初期遅延モニタリング部4と、位相比較部5と、遅延制御部6と、ファイン遅延部7とを備え、初期遅延モニタリング部4は、基準クロックと複数の単位遅延部のうちの一部の単位遅延部が出力する単位遅延クロックとの位相を比較する複数の位相比較用フリップフロップを備え、これら位相比較用フリップフロップの数を単位として当該比較を段階的に繰り返すことにより、全範囲について初期遅延モニタリングを行うものである。

(もっと読む)

半導体装置

【課題】電流消費を削減する。

【解決手段】第1のクロック信号(ICLK)を受け、第1のクロック信号を可変である遅延量に応じて遅延させた第2のクロック信号(LCLK)を出力する遅延回路(31)と、第2のクロック信号を受け、遅延された第3のクロック信号(RCLK)を出力するレプリカ回路(32)と、第1および第3のクロック信号の位相差が所定時間以上であるか否かを検知し、所定時間以上である場合には遅延回路の遅延量を変化させ、所定時間未満である場合には遅延回路の遅延量を変化させないように制御する位相差検出回路(36)と、を備える。

(もっと読む)

位相調整回路及び位相調整方法

【課題】LSIチップ面積の増大を抑制しつつ、製造ばらつきや使用条件の影響を受けない安定的な位相調整を実現する

【解決手段】入力クロックと出力クロックの位相差を調整する位相調整回路を以下のように構成する。その位相調整回路は、出力クロックに遅延を付加するクロック遅延回路と、入力クロック、もしくは、入力クロックと出力クロックの位相差のパルスを入力として受け、パルス除去幅設定値によって遅延素子の段数を変化させて、入力クロック、もしくは、入力クロックと出力クロックの位相差のパルスの幅を検出する位相差検出回路とを有することが好ましい。そして、位相差検出回路で検出した入力クロックと出力クロックの位相差が入力クロックに対して目標の位相差になるようにクロック遅延回路にて出力クロックに遅延を付加する。

(もっと読む)

半導体装置

【課題】出力クロック信号を生成して出力するまでに要する時間を短縮させる。

【解決手段】半導体装置は、第1のクロック信号のライズエッジ及び第2のクロック信号のライズエッジを合成して第1及び第2のクロック信号のライズエッジの間にライズエッジを有する第3のクロック信号を生成する第1の位相合成回路と、第1のクロック信号のフォールエッジ及び第2のクロック信号のフォールエッジを合成して第1及び第2のクロック信号のフォールエッジの間にフォールエッジを有する第4のクロック信号を生成する第2の位相合成回路と、第3のクロック信号のライズエッジを受けてライズ/フォールエッジの内の一方の位相を、第4のクロック信号のフォールエッジを受けてライズ/フォールエッジの内の他方の位相を其々調整した出力クロック信号を出力する第3の位相合成回路と、を備える。

(もっと読む)

半導体装置及びその制御方法

【課題】クロック信号にジッタ成分が重畳している場合であってもDLL回路を正しくロックさせる。

【解決手段】カウンタ部102のカウント値に応じてクロック信号LCLKを生成するディレイライン101と、クロック信号LCLKを反転させるか否かを制御する反転制御部103とを備える。カウンタ部102のカウント値を第1の初期値にリセットした後、反転制御部103はクロック信号LCLKを反転させ又は反転させることなく出力する。次に、カウンタ部102のカウント値を第2の初期値にリセットする。本発明によれば、ジッタなどの影響によってクロック信号LCLKを誤って反転させ、或いは誤って反転させなかった場合であっても、ダウンカウント(またはアップカウント)が多数回連続することがなくなる。これにより、第1及び第2の初期値としてオフセットした値を用いることが可能となる。

(もっと読む)

半導体装置

【課題】DLL回路がロックしないという現象の発生を防止する。

【解決手段】カウンタ回路202と、カウンタ回路202のカウント値CNTに応じた遅延量を内部クロック信号LCLKに与えるディレイライン201とを有する。まず、カウンタ回路202は第1のカウント値にセットされ、判定信号PDに基づいてそのカウント値CNTが周期的に更新される。その結果、内部クロック信号LCLKの位相が所望の位相に到達しなかった場合、カウンタ回路202は、第1のカウント値とは異なる第2のカウント値にセットされ、DLL回路200がリスタートされる。これにより、DLL回路がロックしなかった場合であっても自動的にリスタートされることから、DLL回路がロックしないという現象が防止される。

(もっと読む)

クロック生成装置および電子機器

【課題】レプリカ回路が不要で、小面積化を図ることが可能であり、しかもジッタの増加を防止でき、低ジッタ出力クロックを生成することが可能なクロック生成装置および電子機器を提供する。

【解決手段】アキュムレータの値に応じて目標とするNCOクロックと実際のNCOクロックとの位相差を取得する位相差取得部と、入力クロックに位相同期した信号に応じて入力クロックに複数の遅延を与えた複数の遅延クロックを生成する遅延同期回路と、位相差取得部の位相差情報を受けて複数の遅延クロックから目標とする上記NCOクロックの位相に近づくような遅延が与えられた遅延クロックを選択し、選択クロックとして出力する選択部と、選択部で選択された上記選択クロックに上記NCOクロックを同期させて出力クロックを得る第2の同期回路とを有する。

(もっと読む)

誤ロック防止回路、防止方法及びそれを利用した遅延ロックループ

【課題】遅延ロックループにおいて誤ロックが生じた場合、そこから抜け出すために使用される誤ロック防止回路、防止方法及びそれを利用した遅延ロックループを提供する。

【解決手段】誤ロック防止回路はハーモニックロックを検出する検出器とスタックロックを検出する検出器とで構成される。ハーモニックロック検出器は前記遅延クロックを本発明の特徴的な方法でサンプリングする複数個のフリップフロップ及び論理部で構成される。ハーモニックロック検出器では基準クロックと基準クロックから遅延された複数個の遅延クロックの立ち上がりエッジを比較してこれらの立ち上がりエッジが基準クロックの1周期から離れた場合を検出する。スタックロック検出器は位相検出器の出力信号と前記遅延クロックのうち1つを利用した論理回路であり、論理演算の結果で位相検出器をリセットさせる。

(もっと読む)

クロック発生回路、表示装置用駆動回路及びクロック発生回路の制御方法

【課題】電源投入時や通常動作時でも、より確実にクロックの生成が停止した状態から回復することが可能となるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路10と、前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路30と、を備えるものである。

(もっと読む)

半導体装置

【課題】DLL回路の調整を素早く完了する。

【解決手段】第1のクロック信号(図2のCLKIN)を遅延させて第2のクロック信号(図2のLCLK)を生成する遅延部(図2の33、34が相当する)と、第1のクロック信号と、第2のクロック信号をさらに遅延した信号(図2のRCLK)との位相を比較する位相比較回路(図2の36)と、遅延部の遅延量を決定するカウント値を遅延部に出力すると共に、位相比較回路の位相比較結果に応じてアップダウンするカウンタ回路(図2の37)と、初期設定動作時において、第1のクロック信号の周期を検知し、検知した周期に応じたカウント値の初期値をカウンタ回路に対して出力する初期遅延量制御回路(図2の30)と、を備える。

(もっと読む)

11 - 20 / 308

[ Back to top ]