国際特許分類[H03L7/081]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 付加的な制御移相器を有するもの (308)

国際特許分類[H03L7/081]に分類される特許

61 - 70 / 308

遅延ロックループ回路、半導体集積回路装置

【課題】低い周波数から高い周波数までの幅広い周波数帯域に対応して、回路面積の小さい遅延ロックループ回路、その遅延ロックループ回路を搭載する半導体集積回路装置を提供する。

【解決手段】遅延ロックループ回路は、位相変更回路と、遅延線回路と、遅延制御回路とを具備する。位相変更回路は、入力される基準クロックに対して第1の位相差を有する第1の信号と、第2の位相差を有する第2の信号とを出力する。第1の位相差と第2の位相差との差分は所定の位相遅延量を示す。遅延線回路は、変更可能な単位遅延量を備える遅延回路を複数含む。遅延制御回路は、単位遅延量の合計が基準位相遅延量になるように単位遅延量を制御する。

(もっと読む)

デジタル制御発振器

【課題】TDCに関する冗長構成を削減可能なDCOを提供する。

【解決手段】DCOは、デジタル制御信号によって遅延量が制御される3以上の奇数個の単相インバータ101〜105を環状に接続したリングオシレータと、単相インバータの各々の出力信号をバッファリングし、第1の差動信号として夫々出力する奇数個のバッファ111〜115と、基準信号の立ち上がりエッジまたは立ち下がりエッジにおける第1の差動信号の値を保持して第2の差動信号として夫々出力する奇数個のフリップフロップ121〜125と、奇数個のフリップフロップから出力される奇数組の第2の差動信号を入力し、奇数組の第2の差動信号を位相の進み順に配列したときの、連続する高レベル値または連続する低レベル値の末尾を示す情報を出力するエッジ検出器130とを具備する。

(もっと読む)

DLL回路

【課題】簡単な構成により、ロックするまでの時間を大幅に短縮化したDLL回路を実現する。

【解決手段】切換回路15によって位相比較器13をDLLループから切り放しておき、第1可変遅延回路11の出力クロックCLK2の立上りエッジによってカウンタ14のカウントを開始し、第1可変遅延回路11への入力クロックCLK1の立上りクロックのエッジによってそのカウントを停止させる。そして、入力クロックCLK1の立上りエッジのタイミングで、切換回路15により位相比較器13をDLLループに接続するとともに、カウンタ14のカウンタ値に相当する段数に、第1可変遅延回路11の遅延セル段数を設定してから、通常のDLLロック動作を行わせる。

(もっと読む)

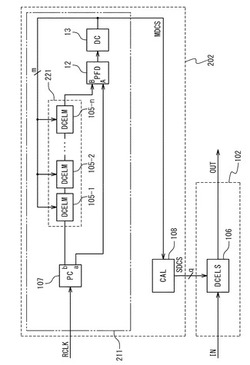

遅延ロックループ回路、信号遅延方法

【課題】回路面積を大きくすることなく、遅延ロックループ回路を提供すること

【解決手段】逓倍PLL107は、基準クロックを逓倍して出力する。DLL211は、逓倍PLL107から出力されたクロックと、逓倍PLL107から出力されたクロックを遅延させたクロックと、を比較し、比較結果に基づいて所定の遅延量を持つ遅延信号を生成する。遅延制御信号演算回路108は、DLL211が生成した遅延信号に基づき、所望の遅延制御信号を生成する。第1の遅延回路102は、遅延制御信号演算回路108が生成した遅延制御信号に基づいて、入力信号を遅延させる。

(もっと読む)

半導体集積回路装置

【課題】プロセスモニタに必要な回路面積を増加させることなく、高精度なプロセスキャリブレーションを短時間で行う。

【解決手段】ディジタル制御発振器38が任意の発振バンドを選択した後、制御部25はTDC41の信号がプロセスモニタ制御部40に入力されるようにスイッチ44を切り換える。TDC41は、信号VREFの立ち上がりエッジと最も近い信号VPREの立ち上がりエッジの期間をディジタル値に、信号VREFの立ち上がりエッジと2番目に近い信号VPREの立ち上がりエッジの期間をディジタル値に変換し、その差を算出する。プロセスモニタ制御部40は、ルックアップテーブルを参照し、算出した値と予め設定されている期待値とを比較し、プロセス値を決定する。そのプロセス値は、プロセス信号として調整制御部26にそれぞれ出力され、プロセスキャリブレーションが行われる。

(もっと読む)

復調器及び通信装置

【課題】受信信号と局部発振信号とに位相差があっても復調できるようにする。

【解決手段】復調器1は、変調器2で送信された受信信号D3をアンテナ11で受信し、この受信した受信信号D3をVCO13に注入して、自走発振周波数を有する局部発振信号D6を発振する。この発振した局部発振信号D6を90度移相器で90度移相する(局部発振信号D7になる)。アンテナ11で受信した受信信号D3の位相と90度移相器で90度移相した局部発振信号D7の位相とを位相比較器15で比較して、局部発振信号D6の位相を調整するための位相調整信号Vctを生成する。この生成した位相調整信号Vctに基づいて、受信信号D3と局部発振信号D6とをVCO13で同期させ、該同期させたものである局部発振信号D8をミキサ17に入力する。注入同期後の局部発振信号D8と受信信号D3とをミキサ17で演算して当該受信信号D3を復調する。

(もっと読む)

周波数逓倍遅延ロックループ

【課題】周波数逓倍回路を提供する。

【解決手段】周波数逓倍回路(100)は、遅延ラインとクロック合成回路(TOG)を備える。遅延ラインは、その一端でリファレンスクロック(102)を受けて、一周期に一致した複数の遅延素子(101)からクロックタップ出力を発生させる。クロック合成回路(TOG)は、一対のタップ出力に応答して、各タップ出力から出力クロックパルスの立ち上がり及び立ち下がりエッジを発生させる。出力クロックの周期は入力クロックの周期よりも短い。遅延ラインは、遅延素子(101)の周期に一致するように遅延ロックループに含まれてもよい。所定数の遅延段タップ出力に接続された入力を有し、相補出力を供給する、複数の合成回路セル(TOG)が設けられる。セレクタ(106)は、位相検出器(112)からの選択制御信号に応答して、合成セルの1つに係る一対の相補出力のうちの一方から出力を選択する。

(もっと読む)

遅延固定ループ回路

【課題】外部電源電圧のレベル変動とは関係なく安定的に遅延固定動作を行う遅延固定ループ回路を提供する。

【解決手段】外部電源電圧のレベルを検出する電圧レベル検出部280と、ソースクロック及びフィードバッククロックの位相を比較する位相比較部200と、電圧レベル検出部280の出力信号に応じて、第1および第2遅延ユニット単位のうち何れか一方を開始遅延ユニット単位として、他方を連結遅延ユニット単位としてそれぞれ指定し、位相比較部200の出力信号に応答して、遅延量が、所定の遅延量までは前記開始遅延ユニット単位で、前記所定の遅延量以後には前記連結遅延ユニット単位で前記ソースクロックを遅延させ、遅延固定クロックDLLCLKとして出力するクロック遅延部220と、前記遅延固定クロックに前記ソースクロックの実際の遅延条件を反映して、前記フィードバッククロックとして出力する遅延複製モデル部240とを備える。

(もっと読む)

DLL回路及びこれを備える半導体装置

【課題】DLL回路のロックに要する時間を短縮する。

【解決手段】外部クロック信号CLKとレプリカクロック信号RCLKの位相差量を検出する位相差量検出回路100と、位相差量に基づいて外部クロック信号CLKを遅延させることにより内部クロック信号LCLKを生成する可変遅延回路21と、内部クロック信号LCLKを遅延させることによりレプリカクロック信号RCLKを生成するレプリカバッファ24とを備える。本発明によれば、外部クロック信号CLKに対してレプリカクロック信号RCLKの位相が進んでいるか或いは遅れているではなく、その位相差量に基づいて可変遅延回路21が制御されることから、位相差量が大きい場合であっても、高速にDLL回路をロックさせることが可能となる。

(もっと読む)

閉ループ・クロック訂正方法および閉ループ・クロック訂正制御システム適応装置

【課題】閉ループ・クロック訂正方法および閉ループ・クロック訂正制御システム適応装置を提供する。

【解決手段】閉ループ・クロック訂正システムおよび方法は、少なくとも1つの同位相クロックおよび少なくとも1つの直交位相クロックを含む2つ以上の入力信号を調整するステップと、調整された直交位相クロック信号を、4象限補間出力クロック位相を生成可能なデバイスに印加するステップとを含む。補間出力クロック位相は、遅延されて測定デバイス用のクロックを形成する。2つ以上の調整された入力信号は、測定デバイス上で補間出力クロック位相の範囲にわたって測定される。測定デバイスからのサンプル情報を使用して、同位相クロックおよび直交位相クロック上の誤差が決定される。同位相クロックおよび直交位相クロックは、決定された誤差情報を使用して適応される。

(もっと読む)

61 - 70 / 308

[ Back to top ]