国際特許分類[H03L7/081]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 付加的な制御移相器を有するもの (308)

国際特許分類[H03L7/081]に分類される特許

71 - 80 / 308

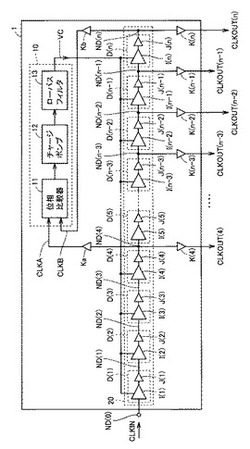

遅延同期ループ回路およびインターフェース回路

【課題】外部クロック信号に対して所定の位相差を有する遅延クロック信号を精度良く生成することができるDLL回路を提供する。

【解決手段】DLL回路1は、制御部10と、第1および第2のノードND(0),ND(n)間に直列接続されたn個(nは2以上の整数)の遅延部D(1)〜D(n)とを含む。第1のノードND(0)には外部クロック信号CLKINが入力される。制御部10は、n個の遅延部D(1)〜D(n)のうち所定の2個の遅延部D(4),D(n)の出力信号CLKA,CLKBの位相差に応じた制御電圧VCを出力する。各遅延部Dは互いに同一の構成を有し、入力された信号に対して制御電圧VCに応じた遅延時間だけ遅延した信号を出力する遅延バッファIと、遅延バッファIの出力を電源電圧の振幅を有する矩形波に整形して出力する整形バッファJとを含む。遅延部D(4)〜D(n)の出力信号が遅延クロック信号として用いられる。

(もっと読む)

タイミング調整回路、タイミング調整方法及び補正値算出方法

【課題】内部クロック信号の位相を高精度に調整するタイミング調整回路、タイミング調整方法及び補正値算出方法を提供すること。

【解決手段】位相調整回路31は、マスタDLL回路11の第1遅延回路21から位相比較回路22までの配線によって生じる遅延時間を補正する第1段数補正値と、スレーブDLL回路12の入力バッファ回路33と出力バッファ回路34によって生じる遅延時間を補正する第2段数補正値を位相調整値Dpに付与する。位相調整回路31は、位相調整値Dpを第2遅延回路32に出力する。第2遅延回路32は、位相調整値Dpに応じた段数のバッファ回路(遅延素子)を直列に接続する。

(もっと読む)

遅延固定ループ回路およびこれを利用した半導体メモリ装置

【課題】入力されるソースクロックREFCLKと、出力される遅延固定クロックDLLCLKとの間の位相差が最大値に達するか否かを検知し、レジスタ制御型遅延固定ループ回路の動作を制御することができる遅延固定ループ回路を提供する。

【解決手段】ソースクロックの位相とフィードバッククロックの位相とを比較し、比較結果に対応して遅延固定信号を生成する位相比較部200と、前記遅延固定信号に応答して、前記ソースクロックを遅延させて遅延固定クロックとして出力し、限界遅延量に達した後にも遅延固定が行われない場合に遅延終了信号を活性化させるクロック遅延部220と、前記遅延固定クロックに前記ソースクロックの実際の出力経路の遅延時間を反映し、前記フィードバッククロックとして出力する遅延複製モデル部240と、前記遅延固定信号および前記遅延終了信号に応答して遅延固定動作を終了させる遅延固定動作制御部250とを備える。

(もっと読む)

遅延回路

【課題】矩形波を入力される遅延回路において、入力信号にノイズパルスが存在すると、出力信号のジッターが生じる。

【解決手段】シュミットコンパレータ102からの出力信号VdoでスイッチSW3を制御し、コンデンサCstへの充電電流を供給する電流源I1と、放電電流を供給する電流源I2とのいずれかを選択する。入力信号VdiでスイッチSW1,SW2を制御することで、選択された電流源からの電流供給がオン/オフされる。シュミットコンパレータ102はコンデンサCstの電圧Vstに応じてVdoを切り替える。Vdiの立ち上がり時には、VdiのHレベル期間にてコンデンサCstへ充電電流を供給し、Vdiの立ち下がり時には、VdiのLレベル期間にてコンデンサCstへ放電電流を供給する。

(もっと読む)

集積回路、集積回路システム、シリアルパラレル変換装置およびスキュー調整方法

【課題】簡単な回路または簡単な処理によりスキュー調整する。

【解決手段】集積回路3は、入力された外クロック信号を遅延させた内クロック信号を出力するクロック遅延回路43と、入力されたデータ信号を内クロック信号によりラッチするラッチ回路45と、クロック遅延回路43に対して、外クロック信号に対する内クロック信号の遅延量として、複数の遅延量を設定する遅延量設定回路58と、複数の遅延量それぞれの設定の下でのラッチ回路45の出力信号を判定するラッチ判定回路52と、ラッチ判定回路52による複数の遅延量それぞれについての複数の判定値を記憶する記憶部53と、記憶部53に記憶された複数の判定値とクロック遅延回路43に設定した複数の遅延量との関係から、クロック遅延回路43による内クロック信号の遅延量を取得する遅延量取得部とを有する。

(もっと読む)

高周波発振源

【課題】発振器を広帯域化しても、発振器の全同調帯域に渡って低位相雑音化を図ることができる高周波発振源を得ることを目的とする。

【解決手段】注入同期電圧制御発振器1の出力波を分配する電力分配器2と、その電力分配器2により分配された出力波を遅延して、遅延後の出力波を注入波として注入同期電圧制御発振器1に帰還させる遅延処理部4とを設け、移相量制御部11が注入同期電圧制御発振器1の出力波と注入同期電圧制御発振器1に帰還される注入波の位相差がゼロになるように、移相器7により出力波に与えられる移相量を制御する。

(もっと読む)

位相調整装置及び無線受信装置

【課題】効率的に且つ低消費電力で目的の信号との位相を調整するのに好適な位相調整装置及び無線受信装置を提供する。

【解決手段】位相調整装置100を、制御電圧によって遅延量を可変可能なインバーター回路IV1〜IVNをループ構成に接続してなる遅延段回路10と、遅延段回路10の遅延量を一定に保持する位相同期用回路20と、遅延段回路10の各接続部に入力端子が電気的に接続された接続切替回路SW1〜SWMを含む接続切替回路群30と、切替制御回路40とを含む構成とし、切替制御回路40は、遅延段回路10における1つおきに且つ周回して順に並ぶ各インバーター回路に対応する接続切替回路を1つずつ選択し、選択した接続切替回路が、遅延信号を後段の回路に供給するように、その他の接続切替回路が遅延信号を後段の回路に供給しないようにする切替制御信号を生成し、これを各接続切替回路に供給する。

(もっと読む)

位相調整装置及び無線受信装置

【課題】効率的に且つ比較的低消費電力で目的の信号との位相を調整するのに好適な位相調整装置及び無線受信装置を提供する。

【解決手段】位相調整装置100を、遅延量を可変可能なインバーター回路IV1〜IVNをループ構成に接続してなる遅延段回路10と、遅延段回路10の遅延量を一定に保持する位相同期用回路20と、遅延段回路10の各接続部に入力端子が電気的に接続された接続切替回路SW1〜SWMを含む接続切替回路群30と、切替制御回路40と、信号出力回路50とを含む構成とし、切替制御回路40は、遅延段回路10における各インバーター回路に対応する接続切替回路を1つずつ且つ周回して選択し、選択した接続切替回路SWからのみ遅延信号を出力するように制御すると共に、偶数番目に選択された接続切替回路SWからの遅延信号を反転して後段の回路に供給するように信号出力回路50を制御する。

(もっと読む)

DLL回路

【課題】LPF出力の変化に対するロック周波数の変化量のゲイン設定のばらつきの抑制でジッタ精度をより向上できるDLL回路の提供。

【解決手段】遅延クロックを生成する遅延回路101と、遅延クロックと入力クロックの位相差信号を出力する位相比較回路10と、位相差信号対応の位相差電圧を出力するチャージポンプ回路20と、チャージポンプ回路出力の高周波成分を除去するローパスフィルタ回路30と、ローパスフィルタ回路の出力電圧を電流に変換する第1電圧−電流変換回路40及び基準電圧Vrefを電流に変換する第2電圧−電流変換回路50を含み、第1電圧−電流変換回路の出力電流から第2電圧−電流変換回路の出力電流を減算した結果を変換した電圧とオフセット電流Idを変換した電圧とを含み、位相差電圧が基準電圧より小の場合、オフセット電流を変換した電圧を制御電圧Vcontとして遅延回路に出力する遅延制御回路102と、を備える。

(もっと読む)

クロック生成回路

【課題】位相ロックの精度を向上する。

【解決手段】クロック生成回路は、出力クロックの周期または位相を段階的に遅延する第1の遅延回路および前記第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有する逓倍回路と、前記逓倍回路内の第1の遅延回路から出力された前記出力クロックを入力し、前記出力クロックを所定時間遅延させる第2の遅延回路および前記第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有する位相同期回路を備え、前記逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタをさらに有し、前記第3のカウンタのカウンタ値が前記第1の値から前記第2の値に変化した時、前記第2の遅延回路の遅延時間が前記第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように前記第2のカウンタのカウンタ値を設定する。

(もっと読む)

71 - 80 / 308

[ Back to top ]